#### CMOS 4-Bit Microcontroller

# **TMP47C834N TMP47C834F**

The TMP47C834 are based on the TLCS-470 CMOS series. The TMP47C834 have on-screen display circuit to display characters and marks which indicate channel or time on TV screen, AD converter (comparator) input, and DA converter output such as TV.

| Part No.   | ROM          | RAM         | Package            | OTP        |

|------------|--------------|-------------|--------------------|------------|

| TMP47C834N | 01020  -:+   | E42 4 bit   | P-SDIP42-600-1.78  | TMP47P834N |

| TMP47C834F | 8192 × 8-bit | 512 × 4-bit | P-QFP44-1414-0.80D | TMP47P834F |

#### **Features**

- ◆4-bit single chip microcomputer

- lacktriangleInstruction execution time: 1.9  $\mu$ s (at 4.2 MHz)

- ◆92 basic instructions

- ◆Table look-up instructions

- ◆Subroutine nesting: 15 levels max

- ◆6 interrupt sources (External: 2, Internal: 4) All sources have independent latches each, and multiple interrupt control is available

- ◆I/O port (30 pins)

- Input 2 ports 5 pins I/O 7ports 25 pins

- ◆Interval Timer

- Two 12-bit Timer / Counters

Timer, event counter, and pulse width measurement mode

- ◆Watchdog timer

- ◆Serial Interface with 8-bit buffer

- Simultaneous transmission and reception capability

- External / internal clock, leading / trailing edge shift, 4/8-bit

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

■ The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments traffic signal instruments control instruments medical instruments. all types of transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

2000-10-19 4-34-29

♦On-screen display circuit

Character patterns:

Characters displayed:

16 columns x 2 lines

• Composition: 8 x 8 dots (smoothing function)

• Size of character: 2 kinds (line by line)

Color of character: 7 kinds (character by character)

Variable display position: horizontal 64 / vertical 64 steps

Double scan mode switching function

◆DA converter (Pulse width modulation) outputs

• 14-bit resolution 1 channel

6-bit resolution 4 channels

◆3-bit AD converter (Comparator) input

Auto frequency control signal (S-shaped curve) detection

◆Pulse output (clock for PLL IC)

♦ Horizontal synchronous signal is detected by timer/counter

◆Remote control signal preprocessing capability

◆High current outputs

LED direct drive capability (typ. 20 mA × 4 bits)

◆HOLD function: Battery / Capacitor back-up

◆Real Time Emulator: BM47C834B

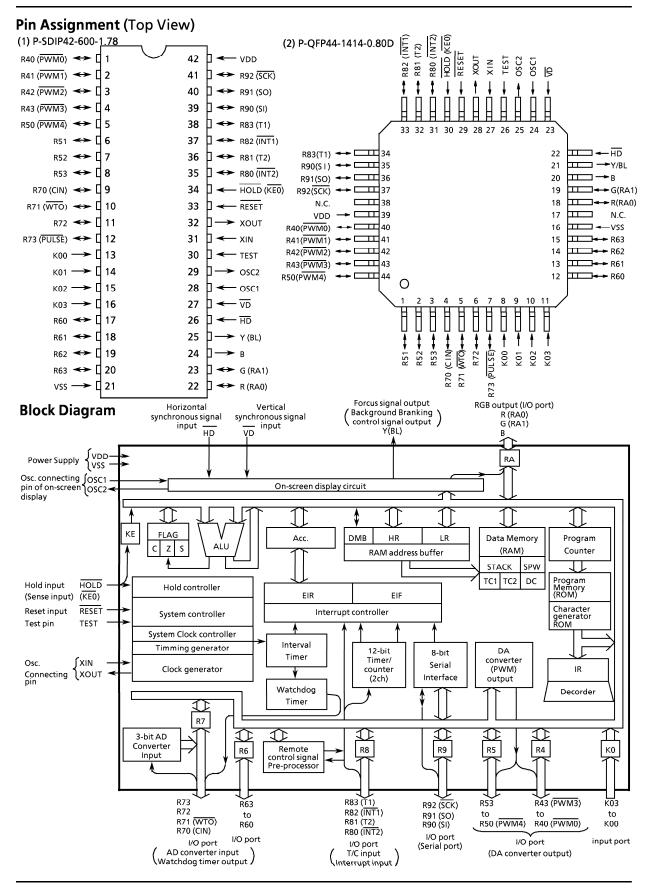

# **Pin Function**

| Pin Name                                  | Input / Output  | I                                                                                                | Functions                                                                          |  |

|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| K03 to K00                                | input           | 4-bit input port                                                                                 |                                                                                    |  |

| R43 (PWM3) to<br>R41 (PWM1)<br>R40 (PWM0) | I/O (output)    | 4-bit I/O port with latch.<br>When used as input port or DA<br>converter outputs pins, the latch | 6-bit DA converter (PWM) output  14-bit DA converter (PWM) output                  |  |

| R53 to R51                                | 1/0             | must be set to "1".                                                                              |                                                                                    |  |

| R50 (PWM4)                                | I/O (output)    |                                                                                                  | 6-bit DA converter (PWM) output                                                    |  |

| R63 to R60                                | 1/0             | 4-bit I/O port with latch.<br>When used as input port, the latch mu                              | ust be set to "1".                                                                 |  |

| R73 (PULSE)                               | I/O (output)    | 4-bit I/O port with latch.                                                                       | PULSE output                                                                       |  |

| R72                                       | 1/0             | When used as input port, watchdog timer output pin, or AD converter                              |                                                                                    |  |

| R71 (WTO)                                 | I/O (output)    | input pin, the latch must be set to                                                              | Watchdog timer output                                                              |  |

| R70 (CIN)                                 | I/O (input)     | 1.                                                                                               | 3-bit AD converter input                                                           |  |

| R83 (T1)                                  |                 | 4-bit I/O port with latch.                                                                       | Timer / counter 1 external input                                                   |  |

| R82 (ĪNT1)                                | 110 (* 1)       | When used as input port, external interrupt input pin, or timer /                                | External interrupt 1 input                                                         |  |

| R81 (T2)                                  | I/O (input)     | counter external input pin, the                                                                  | Timer / counter 2 external input                                                   |  |

| R80 (ĪNT2)                                |                 | latch must be set to "1".                                                                        | External interrupt 2 input                                                         |  |

| R92 (SCK)                                 | I/O (I/O)       | 3-bit I/O port with latch.                                                                       | Serial clock I/O                                                                   |  |

| R91 (SO)                                  | I/O (output)    | When used as input port or serial port, the latch must be set to "1".                            | Serial data output                                                                 |  |

| R90 (SI)                                  | I/O (input)     | porty the later mast be set to 1.                                                                | Serial data input                                                                  |  |

| G (RA1)<br>R (RA0)                        | Output (I/O)    | RGB output                                                                                       | 2-bit I/O port with latch.  When used as input port, the latch must be set to "1". |  |

| В                                         | Output          |                                                                                                  |                                                                                    |  |

| Y (BL)                                    | Output (output) | Focus signal output                                                                              | Background blanking control signal output                                          |  |

| HD, VD                                    | Input           | Horizontal synchronous signal input,                                                             | Vertical synchronous signal input                                                  |  |

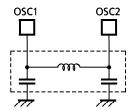

| OSC1, OSC2                                | input, output   | Resonator connecting pin of on-screer                                                            | n display circuit                                                                  |  |

| XIN, XOUT                                 | input, output   | Resonator connecting pin. For inputting external clock, XIN is us                                | used and XOUT is opened.                                                           |  |

| RESET                                     | input           | Reset signal input                                                                               |                                                                                    |  |

| HOLD (KEO)                                | input (input)   | HOLD request/release signal input                                                                | Sense input                                                                        |  |

| TEST                                      | input           | Test pin for out-going test. Be opened                                                           | d or fixed to low level.                                                           |  |

| VDD                                       | Davis           | + 5 V                                                                                            |                                                                                    |  |

| VSS                                       | Power supply    | 0 V (GND)                                                                                        |                                                                                    |  |

#### **Operational Description**

Concerning the TMP47C834 the configuration and functions of hardware are described.

As the description has been provided with priority on those parts differing from the TMP47C834, the technical data sheets for the TMP47C834 shall all so be referred to.

#### 1. System Configuration

◆ Internal CPU Function

They are the same as those of the TMP47C860 except system clock controller.

- Peripheral Hardware Function

- Input / Output Ports

- ② Interval Timer

- ③ Timer / Counters (TC1, TC2)

- 4 Watchdot Timer

- ⑤ Remote Control pulse detector

- 6 On-screen display (OSD) control circuit

- AD converter (comparator) input

- DA converter (Pulse Width Modulation) output

- 9 Pulse output circuit

The description has been provide with priority on functions (①, ⑥, ⑦, ⑧ and ⑨) added to and changed from TMP47C860.

#### 2. Internal CPU Function

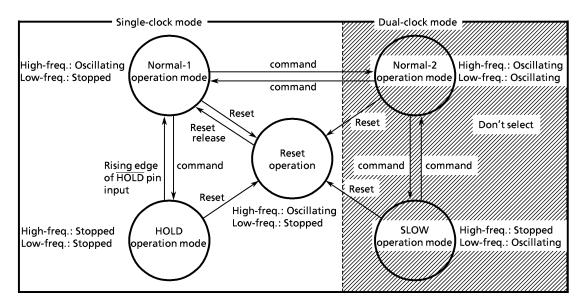

## 2.1 Operation clock control

On the TMP47C834 only single clock mode is available. As single clock mode is automatically selected at the initilization, there is no necessary to set system clock control command register (OP16).

After reset, TMP47C834 is placed in the single-clock mode.

Only the normal 1 operating mode can be active.

Figure 2-1. Operation mode transition diagram

# 3. Peripheral Hardware Function

## 3.1 I/O ports

The TMP47C834 have 9 I/O ports (30 pins) each as follows.

① K0 ; 4-bit input

② R4, R5; 4-bit input / output (shared with pulse width modulation output)

3 R6 ; 4-bit input / output

R7 ; 4-bit input / output (shared with comparator input and watchdog timer output)

© R8; 4-bit input / output (shared with external interrupt input and timer / counter input)

© R9; 3-bit input / output (shared with serial port)

② RA ; 2-bit input / output (shared with on-screen display output)

The description has been provide with priority on functions (② and ④) added to and changed from TMP47C860, and it describes port of ⑦, which item of on-screen display circuit.

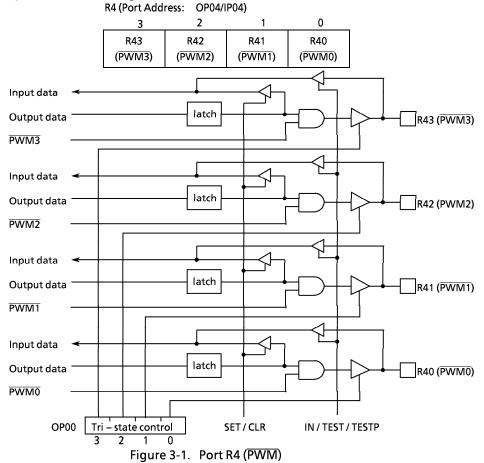

#### (1) Port R4 (R43 to R40)

This is a 4-bit I/O port with latch. It is a port common to DA converter(PWM) output port. R4 port output buffers are Tri-state, and each bit of them can be controlled independently by the program. Controlling the Tri-state is performed by the command register accessed as port address OP00. When some bit of the OP00 is 0, the corresponding bit of the output buffers becomes high impedance state. The output latch should be set to "1" when the port is used as PWM output port, the PWM output should be to "H" level(PWM data is all "0") when the port is used as R 4 port. The output buffers should be set to high impedance state, when the port is used as input port. And the R4 output latch be set to "1", PWM output be set to "High" level, and the output buffer be set to High-Inpedance state during reset.

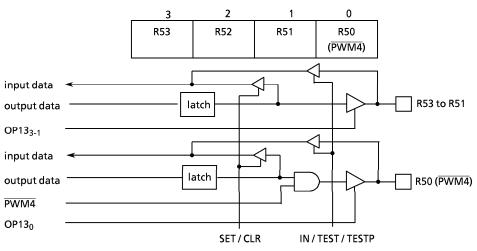

#### (2) Port R5 (R53 to R50)

The 4-bit I/O port with latch. The only R50 pin share DA converter (PWM) output. The port output buffers are tri-state, and each bit of them can be controlled independently by the program. Controlling the tri-state is performed by the command register accessed as port address OP13.

Example: LD A,#1111<sub>B</sub> ; OP13  $\leftarrow$  1111<sub>B</sub>

OUT A,%OP13

OUT #05H,%OP05; R5 port  $\leftarrow$  5H

R5 Port (Port Address: OP05 / IP05)

Figure 3-2. Port R5

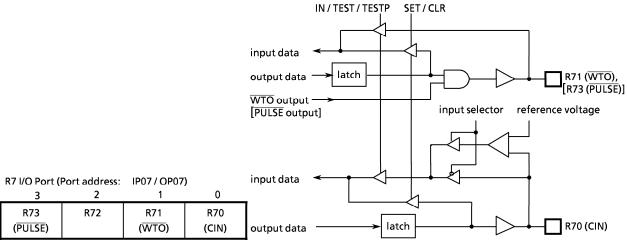

#### (3) Port R7 (R73 to R70)

The 4-bit I/O port with latch. When used as an input port, the latch should be set to "1". The latch is initialized to "1" during reset. R72 pins is I/O port usually.

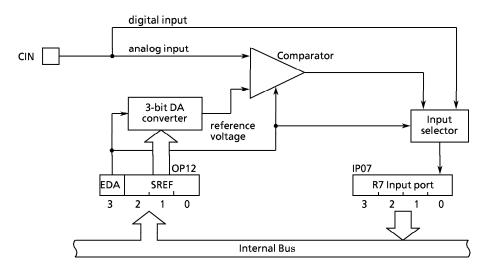

Pin R70 (CIN) is shared with the digital input usual and the AD converter (comparator) input for Auto Frequency Control signal detection. CIN input is comparator input and setting of 3-bit DIA convert for reference voltage are performed by the command register. R71 (WTO), R73 (PULSE) pins are shared with the watchdog timer output and pulse output. R70, R71, R73 pins latch is initialized to "1" during reset, and they are able to use I/O port usually.

Figure 3-3. Port R7

Table 3-1. Port address assignments and available I/O instructions

|                 |                            |                                                      |                        |                         | 3/1        | VO instruction |                        |                           |                                 |

|-----------------|----------------------------|------------------------------------------------------|------------------------|-------------------------|------------|----------------|------------------------|---------------------------|---------------------------------|

| Port            |                            | Port                                                 |                        |                         |            |                |                        |                           | SET @                           |

| Address<br>(**) | Input (IP**)               | Output (OP**)                                        | IN %p, A<br>IN %p, @HL | OUT A, %p<br>OUT @HL,%p | OUT #k, %p | оотв@нг        | SET %p, b<br>CLR %p, b | TEST %p, b<br>TESTP %p, b | SEI (CLR<br>CLR (CL<br>TEST (CL |

| н00             | K0 input port              | Tri—state(R4 port)control                            | 0                      | 0                       | 0          | ł              | 1                      | 0                         | ŀ                               |

| 10              |                            |                                                      | ı                      | J                       | ı          | ı              | ı                      | 1                         | ı                               |

| 02              |                            |                                                      | 1                      | I                       | 1          | ı              | I                      | ı                         | 1                               |

| 03              |                            |                                                      | ı                      | I                       | I          | ı              | ł                      | ı                         | ı                               |

| 04              | R4 input port              | R4 output port                                       | 0                      | 0                       | 0          | ı              | 0                      | 0                         | 0                               |

| 0.5             | R5 input port              | R5 output port                                       | 0                      | 0                       | 0          | 1              | 0                      | 0                         | 0                               |

| 90              | R6 input port              | R6 output port                                       | 0                      | 0                       | 0          | 1              | 0                      | 0                         | 0                               |

| 07              | R7 input port              | R7 output port                                       | 0(                     | 0(                      | 0(         | ı              | 0(                     | 0(                        | 0                               |

| 80              | R8 input port              | R8 output port                                       | ) (                    | Э(                      | ) (        | I              | Э(                     | Э.                        | 1                               |

| 60              | R9 input port              | R9 output port                                       | 0 '                    | 0 1                     | 0 1        | I              | 0                      | 0                         | ł                               |

| 0<br>V          | RA input port              | RA output port                                       | 0                      | 0                       | 0          | 1              | 0                      | 0                         | 1                               |

| 0B              |                            |                                                      | 1                      | 1                       | 1          | 1              | ı                      | ı                         | I                               |

| 00              |                            | OSD command selector                                 | 1                      | 0                       | 0          | 1              | I                      | ı                         | ı                               |

| 5               | Remote control count value | Remote control offset valve                          | С                      | С                       | С          | ı              | I                      | ı                         | ı                               |

| )               | register                   | register                                             | )                      | )                       | )          |                |                        |                           |                                 |

| OE.             | status input (Note 2)      | Remote control single                                | 0                      | 0                       | 0          | ı              | 1                      | 0                         | ı                               |

| 96              | Serial receive buffer      | preprocess circuit control<br>Serial transmit buffer | 0                      | 0                       | 0          | I              | I                      | I                         | 1                               |

| 10H             | undefined                  | Hold operation mode                                  |                        | 0                       |            |                | 1                      | -                         | 1                               |

| : 11            | undefined                  |                                                      | -                      | ı                       | ı          | ı              | I                      | 1                         | I                               |

| 12              | undefined                  | AD converter input control                           | 1                      | 0                       | ŀ          | 1              | 1                      | ı                         | ı                               |

| 13              | undefined                  | Tri-state (R5 port) control                          | 1                      | 0                       | 1          | ı              | 1                      | ı                         | I                               |

| 14              | undefined                  |                                                      | l                      |                         | ı          | I              | I                      | ı                         | I                               |

| 15              | undefined                  | Watchdog timer control                               | l                      | 0                       | 1          | 1              | I                      | ı                         |                                 |

| 16              | undefined                  | 1                                                    | ı                      | 1                       | 1          | ı              | 1                      | I                         | ı                               |

| 17              | undefined                  | PWM buffer selector                                  | 1                      | 0                       | 1          | 1              | 1                      | ı                         | l                               |

| 18              | undefined                  | PWM data transfer buffer                             | I                      | 0                       | ı          | I              | 1                      | I                         | ı                               |

| 19              | undefined                  | Interval timer interrupt control                     | I                      | 0                       | 1          | 1              | I                      | ı                         | l                               |

| 1               | undefined                  | OSD control                                          | l                      | 0                       | ı          | 1              | ı                      | ı                         | I                               |

| 18              | undefined                  |                                                      | ı                      | I                       | ı          | 1              | 1                      | ı                         |                                 |

| Ų               | undefined                  | Timer/counter 1 control                              | l                      | 0                       | ı          | ı              | I                      | ı                         | I                               |

| <u>1</u>        | undefined                  | Timer/counter 2 control                              | l                      | 0                       | ı          | ı              | I                      | 1                         | ı                               |

| 1E              | undefined                  | SIO control 1                                        | I                      | 0                       | I          | ı              | 1                      | ı                         | 1                               |

| <u></u>         | undefined                  | SIO control 2                                        |                        | 0                       | ı          |                | 1                      | 1                         | 1                               |

Note 1: "——" means the reserved state. Unavailable for the user programs. Note 2: the status input of serial interface, clock generator, and HOLD (KEO) pin.

# 3.2 On-screen display (OSD) circuit

An on-screen display (OSD) circuit used to display characters and symbols in built into the TV screen. A maximum of 32 characters, as 16 columns × 2 lines, out of 62 character patterns can be displayed at a time.

#### 3.2.1 OSD circuit function

- Number of characters

- ② Number of characters displayed

- 3 Composition of a character

- 4 Size of character

- **⑤** Color of character

- 6 Display position variable

- 7 Double Scan mode switching function

62 kinds

32 characters (16 columns x 2 lines)

$8 \times 8$  dots (with smoothing function)

2 kinds (selectable line by line)

7 kinds (selectable character by character)

horizontal 64 steps, vertical 64 steps

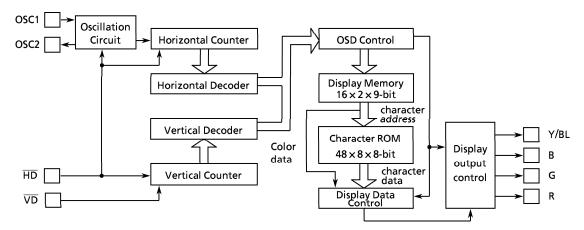

# 3.2.2 OSD circuit configuration

Figure 3-4. OSD circuit

#### 3.2.3 OSD circuit control

The OSD circuit is controlled by the command selector (OPOC) and control register (OP1A). Table 3-2 shows the relationship between OPOC and OP1A. OP1A is multiplexed with the six output control registers which control the display start position, color of character and character size of character, and the two transfer control registers which transter character data to the display memory.

The output control registers consist of 8 bits and all bits can be written by accessing OP1A two times. However, the second access is not required unless the second data are changed. The addressed "0 to 5" are assigned to the six output control registers. OP1A can be accessed by writing the address of the control register where data are to be changed to OP0C. The transfer control registers can be accessed by writing "6" or "7" to OP0C. The transfer control registers have a 12-bit configuration and can access OP1A three times succession. The first access sets which column is displayed within one line 16 columns.

The second and third accesses written 6 bit of character data.

The display memory has a 16-columns  $\times$  9-bit  $\times$  2 lines configuration with a one-to-one correspondence to the number of columns displayed on the screen. The display data consist of 6 character data bits and 3 color data bits for a total of 9 bits. When "6" is written to OPOC, line 1 is stored to the display memory, when "7" is written to OPOC, line 2 is stored. That is after accessing OPOC, the character data specified the second and third times are written to the display memory area specified in the first OP1A access together with the color data loaded to control register DCR50. Thus color can be specified for each character. After setting of all control registers is completed, the character data read from the character ROM(00 to 2F<sub>H</sub>)are output to the R, G and B pins together with the color data by setting OPOC to "F".

Note: The writing a data from display memory is prior than the reading. Therefore, if a data is written to the display memory until the display line is displaying, the display is incorrect.

A data must be written to display memeory when the display is off or when one and two display line are not displayed.

Table 3-2. OSD control commands and control registers

| OSD command     |                                                                             | SD control   | register to  | he accesse   | ed through    | ΟP1Δ           |  |

|-----------------|-----------------------------------------------------------------------------|--------------|--------------|--------------|---------------|----------------|--|

| selector (OPOC) |                                                                             | SD COITGO    | register to  | be accesse   | a anough      | OF IA          |  |

|                 | Control for the h                                                           | norizontal s | tart positio | on of the fi | rst display   | line           |  |

|                 |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 0               | DCR00                                                                       | _            | _            | HS15         | HS14          | (1st access)   |  |

|                 | DCR01                                                                       | HS13         | HS12         | HS11         | HS10          | (2st access)   |  |

|                 | Control for the v                                                           | ertical star | t position o | of the first | display line  | ?              |  |

| 4               |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 1               | DCR10                                                                       | _            | _            | VS15         | VS14          | (1st access)   |  |

|                 | DCR11                                                                       | VS13         | VS12         | VS11         | VS10          | (2st access)   |  |

|                 | Control for the horizontal start position of the second display line.       |              |              |              |               |                |  |

| 2               |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 2               | DCR20                                                                       | _            | _            | HS25         | HS24          | (1st access)   |  |

|                 | DCR21                                                                       | HS23         | HS22         | HS21         | HS20          | (2st access)   |  |

|                 | Control for the v                                                           | ertical star | t position o | of the seco  | nd display l  | ine.           |  |

|                 |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 3               | DCR30                                                                       | _            | _            | VS25         | VS24          | (1st access)   |  |

|                 | DCR31                                                                       | VS23         | VS22         | VS21         | V\$20         | (2st access)   |  |

|                 | Control for the character sizes, smoothing switch and OSD output polarities |              |              |              |               |                |  |

|                 |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 4               | DCR40                                                                       | CS21         | CS20         | CS11         | CS10          | (1st access)   |  |

|                 | DCR41                                                                       | ESMZ         | BLIV         | YIV          | RGBIV         | (2st access)   |  |

|                 | Control for the o                                                           | olor registe | er and OSD   | output bu    | ffers'tri-sta | ate'           |  |

| _               |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 5               | DCR50                                                                       | _            | RDT          | GDT          | BDT           | (1st access)   |  |

|                 | DCR51                                                                       | EBF3         | EBF2         | EBF1         | EBF0          | (2st access)   |  |

|                 | display memory                                                              | write mod    | e for the fi | rst display  | line(addres   | s 00 to 0F)    |  |

|                 |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 6               |                                                                             | DMA3         | DMA2         | DMA1         | DMA0          | (1st access)   |  |

|                 |                                                                             | _            | _            | CRA5         | CRA4          | (2st access)   |  |

|                 |                                                                             | CRA3         | CRA2         | CRA1         | CRA0          | (3st access)   |  |

|                 | display memory                                                              | write mod    | e for the se | cond displ   | ay line(add   | ress 10 to 1F) |  |

|                 |                                                                             | 3            | 2            | 1            | 0             |                |  |

| 7               |                                                                             | DMA3         | DMA2         | DMA1         | DMA0          | (1st access)   |  |

|                 |                                                                             | _            | _            | CRA5         | CRA4          | (2st access)   |  |

|                 |                                                                             | CRA3         | CRA2         | CRA1         | CRA0          | (3st access)   |  |

| E               | display OFF                                                                 |              |              |              |               |                |  |

| <u> </u>        | uispidy Off                                                                 |              |              |              |               |                |  |

| F               | display ON                                                                  |              |              |              |               |                |  |

|                 |                                                                             |              |              |              |               |                |  |

# 3.2.4 Configuration of display character

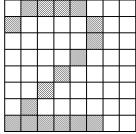

(1) Composition of character and smoothing function

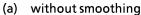

Each character is compsited by 8 x 8 dots. Each dot corresponds to a bit in the character ROM. Figure 3-5. (a) shows an example Composition of a character.

Smoothing function is the function to make characters look smooth. In the time the smoothing function is enabled, additional dots are displayed in the middle of the place where two dots contact each other only at a corner. Controlling of the smoothing function is performed by ESMZ in the OSD control register DCR41. Figure 3-5. (b) shows an example of the smoothing function.

(b) with smoothing

Figure 3-5. Composition of character and smoothing function

(2) Character size and color to display

Size of the characters displayed on screen is selectable line by line from 2 sizes. The size of the first and second display line is disignated by CS11 to CS10 and CS21 to CS20 in the OSD control register DCR40, respectively.

Table 3-3 shows the setting values and character sizes of DCR40.

Table 3-4 shows the display character sizes.

One out of seven colors can be selected for each character to be displayed and are determined by RDT,GDT,and BDT of DCR50. The color data are written to the display memory automatically at the same time as character data are written

Table 3-3. Designation of character size

| Character size  | seco<br>displa | ond<br>ay line |      | rst<br>ay line |

|-----------------|----------------|----------------|------|----------------|

| (DCR40)         | CS21           | CS20           | CS11 | CS10           |

| small character | 1              | 0              | 1    | 0              |

| large character | 0              | 1              | 0    | 1              |

| display OFF     | 0              | 0              | 0    | 0              |

Table 3-4. Character size.

|                | small character                        | large character                        |

|----------------|----------------------------------------|----------------------------------------|

| dot size       | 2T <sub>HD</sub> × 2T <sub>OSC</sub>   | 4T <sub>HD</sub> × 4T <sub>OSC</sub>   |

| character size | 16T <sub>HD</sub> × 16T <sub>OSC</sub> | 32T <sub>HD</sub> × 32T <sub>OSC</sub> |

Note:  $T_{HD}$ : the period of horizontal synchrorous signal  $T_{OSC}$ : the period of OSD clock oscillation

Table 3-5. Select of color to display

| colors<br>displayed | color | data(DC | :R50) |

|---------------------|-------|---------|-------|

| on screen           | RDT   | GDT     | BDT   |

| Blank               | 0     | 0       | 0     |

| Blue                | 0     | 0       | 1     |

| Green               | 0     | 1       | 0     |

| Sian                | 0     | 1       | 1     |

| Red                 | 1     | 0       | 0     |

| Mazenda             | 1     | 0       | 1     |

| Yellow              | 1     | 1       | 0     |

| White               | 1     | 1       | 1     |

Note: Color to display: RGB pin uses Red, Green, Blue such as.

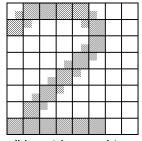

#### 3.2.5 Display start position

Display start position of each display line on screen can be shifted by software.

The vertical and horizontal display starting position for the first line is determined by HS10 to 15 and VS10 to 15 of DCR00 to 11.

The vertical and horizontal display starting position for the second line is determined by HS20 to 25 and VS20 to 25 of DCR20 to 31. Each has a resolution of 64 steps.

The control register and display line on screen are shown in Table 3-6.

Figure 3-6. TV screen image

Table 3-6. Display start position

| Symbol       | Contents                                                                                                                                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS10 to HS15 | horizontal start position of the first display line $HS1 = ((32 \times HS15 + 16 \times HS14 + 8 \times HS13 + 4 \times HS12 + 2 \times HS11 + HS10) \times 4 + X) T_{OSC}$  |

| VS10 to VS15 | vertical start position of the first display line $VS1 = (32 \times VS15 + 16 \times VS14 + 8 \times VS13 + 4 \times VS12 + 2 \times VS11 + VS10) \times 4T_{HD}$            |

| HS20 to HS25 | horizontal start position of the second display line $HS2 = ((32 \times HS25 + 16 \times HS24 + 8 \times HS23 + 4 \times HS22 + 2 \times HS21 + HS20) \times 4 + X) T_{OSC}$ |

| VS20 to VS25 | vertical start position of the second display line<br>VS2 = (32 × VS25 + 16 × VS24 + 8 × VS23 + 4 × VS22 + 2 × VS21 + VS20) × 4T <sub>HD</sub>                               |

Note: X; X is 17 when small character. X is 34 when large character.

\* The vertical display positions of lines 1 and 2 can be specified independently but, to prevent overlapping of the two lines on the display, the value for the vertical display position of line 2 must satisfy ( VS2>VS1+CS11×16T<sub>HD</sub>+CS10×32T<sub>HD</sub>) .

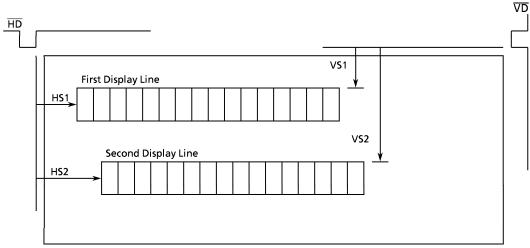

# 3.2.4 Y/BL signal

The Y signal (the logical or output of the R, G and B signals) makes the display clearer by deleting the background only where characters are displayed. The BL signal deletes the entire background for one character ( $8 \times 8$  dots) and is output for all data except that at address  $2F_H$  in the character ROM.

The Y/BL pin is used for both Y signal and BL signal output. Which of the two signals is to be output is determined by the upper 2 bits of OPOA. The dotted lines in Figure 3-7 show the Y/BL signal output being scanned.

Figure 3-7. Example of Y and BL signal output

# 3.2.5 Control of OSD outputs buffer

The OSD outputs for Y,BL and RGB use tri-state output buffers for which the respective polarities can be inverted. Polarity is controlled by DRC41 and tri-state is controlled by DRC51. Bit 3 of DRC41 is used for controlling the smoothing function.

| register | bit | symbol | output<br>name | data "0"          | data "1"         |

|----------|-----|--------|----------------|-------------------|------------------|

|          | 3   | ESMZ   |                | smoozing OFF      | smoozing ON      |

| DRC41    | 2   | BLIV   | BL             | active High       | active Low       |

| DRC41    | 1   | YIV    | Υ              | active High       | active Low       |

| 0        | 0   | RGBIV  | RGB            | active High       | active Low       |

|          | 3   | EBF3   | Y/BL           | output buffer OFF | output buffer ON |

| DRC51    | 2   | EBF2   | В              | output buffer OFF | output buffer ON |

| וכאו     | 1   | EBF1   | G              | output buffer OFF | output buffer ON |

|          | 0   | EBF0   | R              | output buffer OFF | output buffer ON |

Table 3-7. Control of OSD output

## 3.2.6 RA Port function

R signal output and G signal output ports are also used as I/O ports. When not used for color signals, use is possible as normal I/O ports. RA port and Y/BL selection is performed by OPOA. Also, the upper 2 bits of IPOA are used to input the OSD display status.

OP0A Port address: OP0A3 OP0A0 OP0A2 OP0A1 RA0 output RA1 output control of OSD output and RA port output pin No. OP0A3 OP0A2 22 24 25 23 0 0 R G В Υ R G ВL 1 RA0 G В Υ RA0 RA1 ВL Port address: IP0A V02 V01 IP0A1 IP0A0 RA0 input

Figure 3-8. Port RA

RA1 input

0: first display line display ON

1: first display line display OFF

0: second display line display ON

1: second display line display OFF

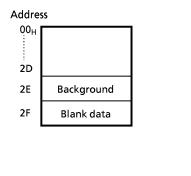

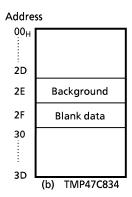

#### 3.2.7 Character ROM

The TMP47C834 can display 62 different 8  $\times$  8 dot characters (character ROM addresses  $00_H$  -  $3D_H$ ). Address  $2F_H$  in the character ROM displays a blank, as with the TMP47C434/634, so set all ROM data to "0".

The first 48 characters of the TMP47C834 character ROM are the same as those of the TMP47C434A/634A; therefore, TMP47C434A/634A programs can be used without change.

(a) TMP47C434A/634A

Figure 3-9. Character ROM configuration

Note: Addresses 3EH and 3FH the character ROM are used in out going test. Data can be not specified by users.

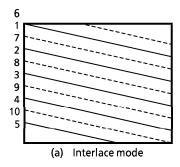

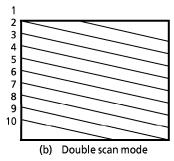

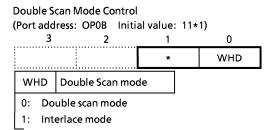

## 3.2.8 Double scan mode switching function

The TMP47C834 has an Double scan mode switching function for selecting the interlace mode or the double scan (non-interlace) mode.

When the double scan mode is used, the number of scan lines on the screen is double that of the interlace mode; therefore, the  $\overline{HD}$  signal is single-stage divided so that the vertical display start position and character size will be the same as with the interlace mode.

In the double scan mode, the horizontal scan line cycle is one-half that of the interlace mode; therefore, it is necessary to increase the OSD oscillation frequency.

Figure 3-10. Double scan mode

# 3.2.9 Double scan mode control

Double scan mode switching is controlled by WHD of the command register OP0B. Setting WHD to "0" selects the double scan mode and setting WHD to "1" selects the interlace mode. The initial setting selects the interlace mode.

Figure 3-11. Double scan mode command register

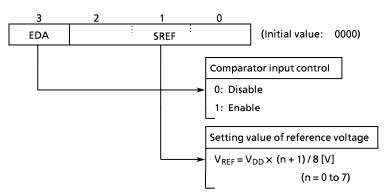

# 3.3 3-bit AD converter (Comparator) input

Comparator input consists of a comparator and a 3-bit DA comvertor. AFC input voltage can be detected in 8 steps by sensing bit 0 of IP07 while cahnging the reference voltage (DA convertor output voltage) with the command register (OP12).

R70 pin is also used for comparator input. Bit 3 is used to set R70 pin for ordinary digital input. The comparator is disabled and bit 3 is set to "0" during reset. The latch should be set to "1" when R70 pin is used for comparator input and digital input.

# 3.3.1 Circuit configuration

The comparator input circuit shown in figure 3-12.

Figure 3-12. Comparator input circuit

#### 3.3.2 Control of comparator input

The reference voltage of the comparator is set using the lower 3 bits of the command register. Table 3-8 shows the reference voltage when  $V_{DD} = 5 \text{ V}$ .

Comparator input control command registor (Port address: OP12)

Figure 3-13. Control command registor

Table 3-8. Reference voltage

| OP12  | Reference   |

|-------|-------------|

| 2 1 0 | voltage [V] |

| 0 0 0 | 0.62        |

| 0 0 1 | 1.25        |

| 0 1 0 | 1.87        |

| 0 1 1 | 2.50        |

| 1 0 0 | 3.12        |

| 1 0 1 | 3.75        |

| 1 1 0 | 4.37        |

| 1 1 1 | 5.00        |

## 3.4 DA converter (PWM) output

The TMP47C434A/634A have five channels built-in DA converter (Pulse width Modulation) outputs. PWM output can easily be obtained by connecting an external low pass filter.

PWM outputs data are multiplex to the R4 port and R50 pin. When the R4 (PWM) port and R50 pin are used for PWM output, the corresponding bits of R4, R50 output latch should be set to "1". The R4, R5 output latch is initialized to "1" during reset.

PWM output is controlled by the buffer selector (OP17) and the data transfer buffer (OP18). PWM data written to the data transfer buffer can be sent to the PWM data latch by writing "C<sub>H</sub>" to the buffer selector, and PWM output PWM output. PWM data transferred to the PWM data latch remain intact until overwritten. Resetting and holding clear the buffer selector, data transfer buffer and PWM data latch to "0" (PWM output is "H" level).

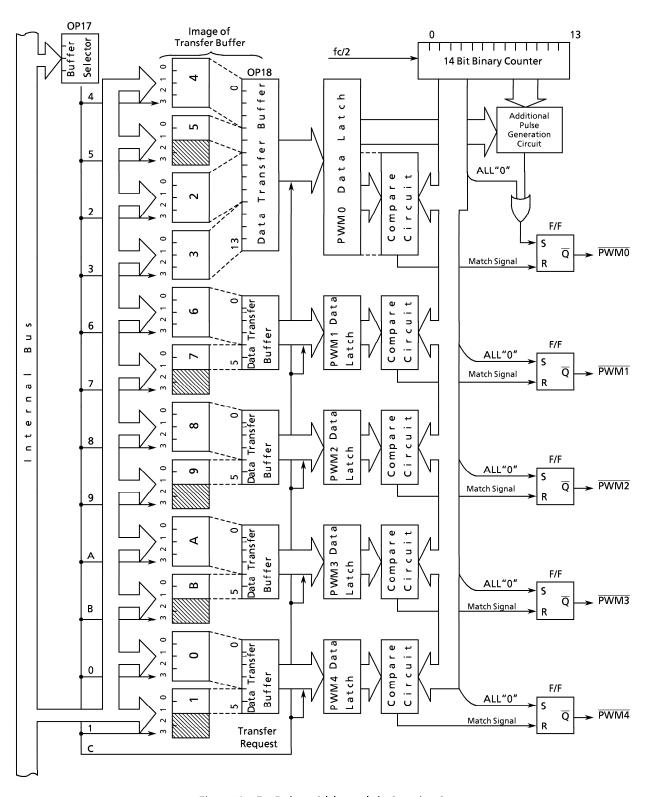

# 3.4.1 Configuration of pulse width modulation circuit

Configuration of pulse width modulation circuit shown in Figure 3-15.

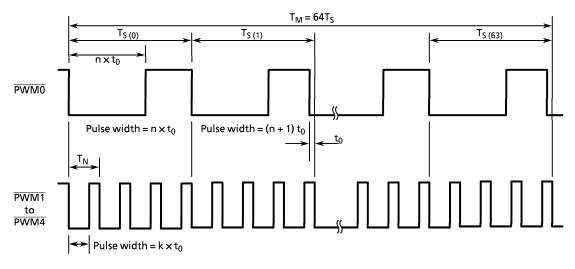

## 3.4.2 Output waveform of PWM circuit

#### (1) PWM0 output

$\overline{PWM0}$  is a PWM output controlled by 14 bits data. The basic period of the  $\overline{PWM0}$  is  $T_M = 2^{15}/fc$ .

The higher 8 bits of 14 bits data are used to control the pulse width of the pulse output with the period of  $T_S = T_M/64$ , which is the sub - period of the  $\overline{PWM0}$ . When the 8 bits data are decimal n (0  $\leq$  n  $\leq$  255), this pulse width becomes n  $\times$  t<sub>0</sub>, where t<sub>0</sub> = 2/fc.

The lower 6 bits of 14 bits data are used to control the generation of an additional  $t_0$  wide pulse in each  $T_S$  period. When the 6 bits data are decimal m ( $0 \le m \le 63$ ), the additional pulse is generated in each of m periods out of 64 periods contained in a  $T_M$  period. The relationship between the 6 bits data and the position of  $T_S$  period where the additional pulse is generated is shown in Table 3-9. (The additional pulse is not generated on  $T_S(0)$ ).

#### (2) PWM1 to PWM4 output

Each of  $\overline{PWM1}$  to  $\overline{PWM4}$  is a PWM output controlled by 6 bits data. The period of them is  $T_M = 2^7/fc$ . When the 6 bits data are decimal k (0<k<63), the pulse width becomes k×t<sub>0</sub>. The waveform is also illustrated in Figure 3-14.

Figure 3-14. PWM output waveform (It is shown to the additional pulse T<sub>5 (1)</sub> and T<sub>5 (63)</sub> of the PWM0)

Figure 3-15. Pulse width modulation circuit

| Bit position of 6 vits data | Relative position of $T_S$ where the output pulse is generated (No. i of $T_{S(i)}$ is listed) |

|-----------------------------|------------------------------------------------------------------------------------------------|

| bit0                        | 32                                                                                             |

| bit1                        | 16, 48                                                                                         |

| bit2                        | 8, 24, 40, 56                                                                                  |

| bit3                        | 4, 12, 20, 28, 36, 44, 52, 60                                                                  |

| bit4                        | 2, 6, 10, 14, 18, 22, 26, 30,, 58, 62                                                          |

| bit5                        | 1, 3, 5, 7, 9, 11, 13, 15, 17,·····, 59, 61, 63                                                |

Table 3-9. Correspondence between 6 bits data and the additional pulse generated T<sub>S</sub> periods

Note: When the corresponding bit is "1", it is output.

# 3.4.3 Control of PWM circuit (Data transfer)

PWM output is controlled by writing output data to a data transfer buffer (OP18). For writing, the output data are divided using the buffer selector (OP17). Buffer numbers are assigned to the data transfer buffers for these divided data, after which the data are written as shown in Table 3-10.

- ① The number of the transfer buffer to which the data are to be written is written to the buffer selector (OP17).

- ② The corresponding PWM data are written to the selected buffer (OP18).

- 3 Operations 1) and 2 are repeated, continuously writing data to the transfer buffer.

- 4 When all of the output data have been written. "CH" is written to the buffer selector.

While the output data are being writen to the transfer buffer, the previously written data are being output. For  $\overline{PWM0}$  output, switching to  $\overline{PWM}$  output occurs at a maximum of  $2^{15}$ /fc [s] (at 4 MHz, 8192fs) after "C<sub>H</sub>" is written to the buffer selector. For  $\overline{PWM1}$  through  $\overline{PWM4}$  output data switching, this requires  $2^{9}$ /fc [s] (at 4 MHz, 128  $\mu$ s).

| Buffer Number<br>(OP17) | Correspondence to<br>(OP18)                                | Mode             | PWM Output     |                                  |

|-------------------------|------------------------------------------------------------|------------------|----------------|----------------------------------|

| 0<br>1                  | Bit of PWM4 transfer buffer<br>Bit of PWM4 transfer buffer | 3 to 0<br>5 to 4 | Write<br>Write | Preceding data<br>Preceding data |

| 2                       | Bit of PWM0 transfer buffer                                | 9 to 6           | Write          | Preceding data                   |

| 3                       | Bit of PWM0 transfer buffer                                | 13 to 10         | Write          | Preceding data                   |

| 4                       | Bit of PWM0 transfer buffer                                | 3 to 0           | Write          | Preceding data                   |

| 5                       | Bit of PWM0 transfer buffer                                | 5 to 4           | Write          | Preceding data                   |

| 6                       | Bit of PWM1 transfer buffer                                | 3 to 0           | Write          | Preceding data                   |

| 7                       | Bit of PWM1 transfer buffer                                | 5 to 4           | Write          | Preceding data                   |

| 8                       | Bit of PWM2 transfer buffer                                | 3 to 0           | Write          | Preceding data                   |

| 9                       | Bit of PWM2 transfer buffer                                | 5 to 4           | Write          | Preceding data                   |

| Α                       | Bit of PWM3 transfer buffer                                | 3 to 0           | Write          | Preceding data                   |

| В                       | Bit of PWM3 transfer buffer                                | 5 to 4           | Write          | Preceding data                   |

| С                       | None                                                       |                  | Transfer       | Present data                     |

Table 3-10. The bit and Buffer number of data transfer Buffer

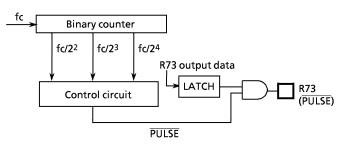

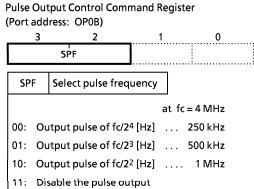

## 3.5 Pulse output circuit

Pulse output circuit generates the pulse clock by dividing the clock frequency to R73 port. The pulse output is used for the basic clock for the PLL IC or peripheral ICs. The pulse output frequency can be set by accessing command register (OPOB). Command register is initialized to "11\*\*" during reset. When R73 port is used as the pulse output, set R73 output latch to "1".

Figure 3-16. Pulse output circuit

Figure 3-17. Pulse output command register

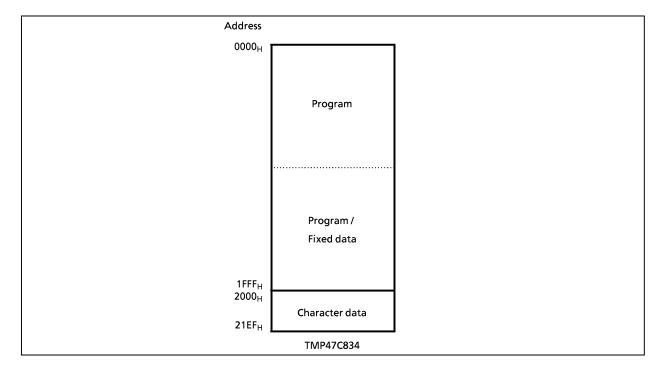

# Notice of ROM code release for masked products

When releasing ROM code for mask products, please take notice as follows,

- (1) The area of program and program / fixed data

- Fill the data "FFH" at all addresses of unused area.

- (2) The area of character data

- $\bullet$  Load the character data at the address 2000H to 21EFH.

- Fill the data "FFH" at all addresses of unused characters.

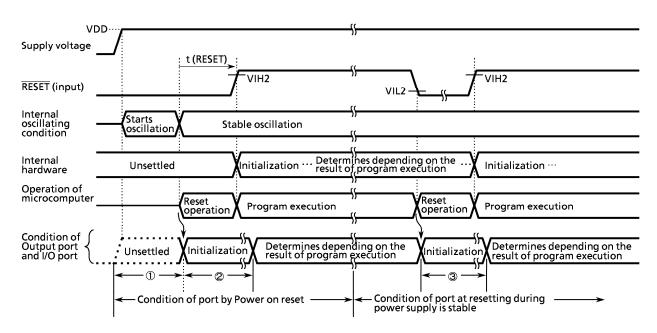

# **Port Condition by RESET Operation**

The transition of Port condition by RESET operation is shown as below.

Figure 3-18. Port condition by Reset operation

- Note 1: t(RESET) > 24/fc

- Note 2: VIL2: Stands for low level input voltage of RESET pin.

- VIH2: Stands for high level input voltage of RESET pin.

- Note 3: The condition of each port is unstable until the reset operation is started (① in the above Figure). Thus, when using port as an output pin, in the term of ①, to prevent the malfunction of external application circuit, insert the circuit outside of microcomputer between the output pin of Port and input pin of external application circuit.

- Note 4: The term starting from reset operation to the program which accesses port is executed (②, ③ in the above Figure), the condition of port becomes on the status of initialization by Reset operation. The initial condition of port differs from I/O circuit by each port, refer to the section of "INPUT/OUTPUT CIRCUITRY". Thus, when using Port as an output pin, in the term of the above ② and ③, the voltage level on the signal that connects with the output pin of Port to the input pin of external application circuit should be determined by the external circuitry such as pull-up resistor and/or pull-down resistor.

# Input / Output Circuitry

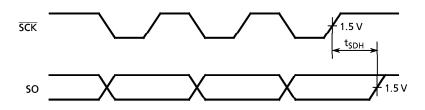

(1) Control Pins

Input / output circuitries of the TMP47C834 control pins are shown below.

| Control Pin  | I/O              | Circuitry                                 | Remarks                                                                                                                                                  |

|--------------|------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN<br>XOUT  | Input<br>Output  | OSC. enable R <sub>f</sub> R <sub>0</sub> | Resonator connecting pins $R = 1 \text{ k}\Omega \text{ (typ.)}$ $R_f = 1.5 \text{ M}\Omega \text{ (typ.)}$ $R_O = 2 \text{ k}\Omega \text{ (typ.)}$     |

| RESET        | Input            | R <sub>IN</sub> R                         | Hysteresis input Contained pull-up resistor $R_{IN} = 220 \ k\Omega \ \ \text{(typ.)}$ $R = 1 \ k\Omega \ \ \text{(typ.)}$                               |

| HOLD (KEO)   | Input<br>(Input) |                                           | Hysteresis input (Sense input) $R = 1 \text{ k}\Omega \text{ (typ.)}$                                                                                    |

| TEST         | Input            | R <sub>IN</sub> R                         | Contained pull-down resistor $R_{IN} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$                                         |

| OSC1<br>OSC2 | Input<br>Output  | OSC. enable  R  R  R  R  R  OSC1  OSC2    | Oscillation terminals for OSD $R = 1 \text{ k}\Omega \text{ (typ.)}$ $R_f = 1.5 \text{ M}\Omega \text{ (typ.)}$ $R_0 = 2 \text{ k}\Omega \text{ (typ.)}$ |

| HD<br>VD     | Input            |                                           | Synchronous signal input Hysteresis input $R=1\ k\Omega\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                             |

# (2) I/O Ports

The input / output circuitries of the TMP47C834 I/O ports are shown below, any one of the circuitries (PB, PC, PF, PU) can be chosen by a code as a mask option.

| Port               | 1/0    | Input / Output Cir            | rcuitry and Code                             | Remarks                                                                                                           |

|--------------------|--------|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| к0                 | Input  | PB  VDD  R <sub>IN</sub> R  R | PC, PF, PU  R <sub>IN</sub>                  | Pull-up or pull-down resistor $R_{IN} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$ |

| R4<br>R50          | I/O    | PB, PC                        | PF, PU                                       | Tri-state or Sink open drain Initial "Hi-Z" $R=1\ k\Omega$ (typ.)                                                 |

| R51<br>R52<br>R53  | I/O    | DISABLE                       | VDD<br>→ → → → → → → → → → → → → → → → → → → | Tri-state Initial "Hi-Z" $R = 1 \text{ k}\Omega \text{ (typ.)}$                                                   |

| R6<br>R8<br>R9     | I/O    | R6                            | R8, R9                                       | Sink open drain Initial "Hi-Z" Hysteresis input (R8, R9) $R = 1 \ k\Omega \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $     |

| R7                 | I/O    | R70 Initial "Hi-Z" R          | R71~R73<br>Initial "High"                    | Sink open drain and push-pull Comparator input (R70 pin) $R=1~k\Omega~(typ.)$                                     |

| R (RA0)<br>G (RA1) | I/O    | PB, PC, PF                    | PU PU                                        | Tri-state Initial "Hi-Z" $R=1~k\Omega$ (typ.)                                                                     |

| B<br>Y (BL)        | Output | OSD status b a                | OSD status b a                               | R, G: Side a<br>B, Y: Side b                                                                                      |

### **Electrical Characteristics**

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

| Parameter                    | Symbol              | Pins                               | Ratings                  | Unit |  |

|------------------------------|---------------------|------------------------------------|--------------------------|------|--|

| Supply Voltage               | $V_{DD}$            |                                    | – 0.3 to 7               | V    |  |

| Input Voltage                | $V_{IN}$            |                                    | $-0.3$ to $V_{DD} + 0.3$ | V    |  |

| Outrout Valtage              | V <sub>OUT1</sub>   | Except sink open drain pin         | $-0.3$ to $V_{DD} + 0.3$ | V    |  |

| Output Voltage               | V <sub>OUT2</sub>   | Sink open drain pin except R7 port | - 0.3 to 10              |      |  |

| Output Gunnant (Ban 1 min)   | I <sub>OUT1</sub>   | R6 port                            | 30                       |      |  |

| Output Current (Per 1 pin)   | I <sub>OUT2</sub>   | R7, R8, R9 port                    | 3.2                      | mA   |  |

| Output Current (Total)       | Σ l <sub>OUT1</sub> | R6 port                            | 60                       | mA   |  |

| Power Dissipation            | PD                  |                                    | 600                      | mW   |  |

| Soldering Temperature (time) | Tsld                |                                    | 260 (10 s)               | °C   |  |

| Storage Temperature          | Tstg                |                                    | – 55 to 125              | °C   |  |

| Operating Temperature        | Topr                |                                    | - 30 to 70               | °C   |  |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant.

Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

Recommended Operating Conditions

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter          | Symbol           | Pins                    | Conditions                           | Min                  | Max                  | Unit  |

|--------------------|------------------|-------------------------|--------------------------------------|----------------------|----------------------|-------|

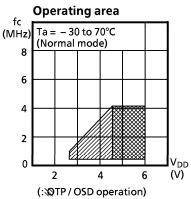

| Cumply Voltage     | \ ,,             |                         | In the Normal mode                   | 4.5                  | 6.0                  | V     |

| Supply Voltage     | $V_{DD}$         |                         | In the HOLD mode                     | 2.0                  | 6.0                  | V     |

| Input High Voltage | V <sub>IH1</sub> | Except Hysteresis Input | V > 4.5.V                            | $V_{DD} \times 0.7$  |                      | >     |

|                    | $V_{\text{IH2}}$ | Hysteresis Input        | $V_{DD} \ge 4.5 V$                   | $V_{DD} \times 0.75$ | $V_{DD}$             |       |

|                    | V <sub>IH3</sub> |                         | $V_{DD} < 4.5 V$ $V_{DD} \times 0.9$ |                      |                      |       |

|                    | $V_{IL1}$        | Except Hysteresis Input | $V_{DD} \ge 4.5 V$                   |                      | $V_{DD} \times 0.3$  |       |

| Input Low Voltage  | $V_{IL2}$        | Hysteresis Input        | V <sub>DD</sub> ≅ 4.5 V              | 0                    | $V_{DD} \times 0.25$ | V     |

|                    | $V_{IL3}$        |                         | $V_{DD}$ < 4.5 V                     |                      | $V_{DD} \times 0.1$  |       |

| Clock Frequency    | fc               |                         |                                      | 0.4                  | 4.2                  | MHz   |

|                    | f <sub>OSD</sub> |                         |                                      | _                    | 6.0                  | IVITZ |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Input voltage  $V_{IH3}$ ,  $V_{IL3}$ : In the SLOW or HOLD mode.

**DC Characteristics**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                           | Symbol           | Pins                                      | Conditions                                           | Min     | Тур. | Max | Unit |  |

|-------------------------------------|------------------|-------------------------------------------|------------------------------------------------------|---------|------|-----|------|--|

| Hysteresis Voltage                  | V <sub>HS</sub>  | Hysteresis Input                          |                                                      | _       | 0.7  | _   | V    |  |

| Input Current                       | I <sub>IN1</sub> | K0 port, TEST,<br>RESET, HOLD             | V <sub>DD</sub> = 5.5 V,                             | _       | _    | ± 2 | μA   |  |

|                                     | I <sub>IN2</sub> | R port (open drain)                       | V <sub>IN</sub> = 5.5 V / 0 V                        |         |      |     | '    |  |

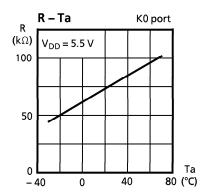

|                                     | R <sub>IN1</sub> | K0 port with pull-up / pull-down          |                                                      | 30      | 70   | 150 |      |  |

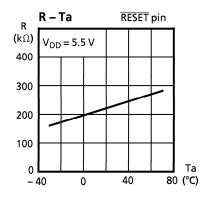

| Input Resistance                    | R <sub>IN2</sub> | RESET                                     |                                                      | 100 220 |      | 450 | kΩ   |  |

| Output leakage<br>Current           | I <sub>LO</sub>  | Tri-state R6, R8, R9 port<br>(open drain) | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V    | _       | _    | ± 2 | μA   |  |

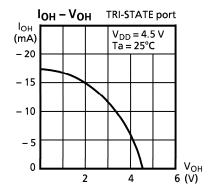

| Output High<br>Voltage              | V <sub>OH2</sub> | R port (tri-state),<br>OSD output         | $V_{DD} = 4.5 \text{ V}, \ I_{OH} = -0.7 \text{ mA}$ | 4.1     | _    | _   | V    |  |

|                                     | V <sub>OL1</sub> | R7, R8, R9 port                           | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$    |         |      |     |      |  |

| Output Low Voltage                  | V <sub>OL2</sub> | R port (tri-state),<br>OSD output         | $V_{DD} = 4.5 \text{ V}, I_{OL} = 0.7 \text{ mA}$    |         | _    | 0.4 | V    |  |

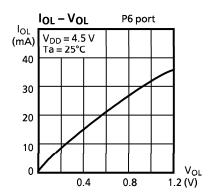

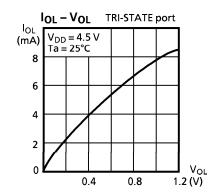

| Output Low Current                  | I <sub>OL</sub>  | R6 port                                   | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$     | _       | 20   | _   | mA   |  |

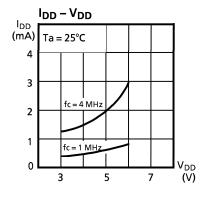

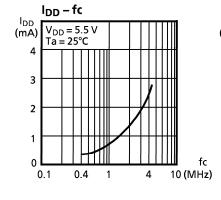

| Supply Current (in the Normal mode) | I <sub>DD</sub>  |                                           | V <sub>DD</sub> = 5.5 V, fc = 4 MHz                  | _       | 3    | 6   | mA   |  |

| Supply Current (in the HOLD mode)   | I <sub>DDH</sub> |                                           | V <sub>DD</sub> = 5.5 V                              | _       | 0.5  | 10  | μA   |  |

Note 1: Typ. values show those at Topr =  $25^{\circ}$ C,  $V_{DD}$  = 5 V.

Note 2: Input Current  $I_{IN1}$ : The current through resistor is not included, when the pull-up / pull-down

resistor is contained.

Note 3: Supply Current:  $V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$

The K0 port is open when the pull-up / pull-down resistor is contained. The voltage applied to the R port is within the valid range  $V_{IL}$  or  $V_{IH}$ .

#### **AD Converter Characteristics**

| Parameter            | Symbol           | Pins | Condition | Min             | Тур. | Max      | Unit |

|----------------------|------------------|------|-----------|-----------------|------|----------|------|

| Analog Input Voltage | V <sub>AIN</sub> | CIN  |           | V <sub>SS</sub> | ı    | $V_{DD}$ | ٧    |

| AD Conversion Error  | _                |      |           | -               | -    | ± 1/4    | LSB  |

**AC Characteristics**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}, Topr = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                    | Symbol           | Condition                      | Min           | Тур. | Max | Unit |

|------------------------------|------------------|--------------------------------|---------------|------|-----|------|

| Instruction Cycle Time       | tcy              |                                | 1.9           | -    | 20  | μS   |

| High level Clock Pulse Width | t <sub>WCH</sub> | For external alock an existing | 90            |      |     |      |

| Low level Clock Pulse Width  | t <sub>WCL</sub> | For external clock operation   | 80            | _    | _   | ns   |

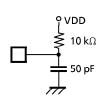

| Shift data Hold Time         | t <sub>SDH</sub> |                                | 0.5 tcy – 0.3 | -    | _   | μs   |

Note: Shift data Hold Time

External circuit for SCK pin and SO pin.

Serial port (Completion of transmission)

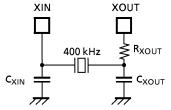

## **Recommended Oscillating Conditions**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

(1) 4 MHz

Ceramic Resonator

CSA4.00MG (MURATA) **KBR-4.00MS**

(KYOCERA)

$C_{XIN} = C_{XOUT} = 30 pF$  $C_{XIN} = C_{XOUT} = 30 pF$

**Crystal Oscillator**

204B-6F 4.0000

(TOYOCOM)

$C_{XIN} = C_{XOUT} = 20 pF$

**Ceramic Resonator**

CSB400B

(MURATA)

$C_{XIN} = C_{XOUT} = 220 pF$ ,

$R_{XOUT} = 6.8 k\Omega$

KBR-400B (KYOCERA)  $C_{XIN} = C_{XOUT} = 100 pF$ ,

$R_{XOUT} = 10 k\Omega$

(3) 32.768 kHz

(VSS = 0 V,

VDD = 2.7 to 6.0 V,

$Topr = -30 \text{ to } 70^{\circ}\text{C})$

CXTIN, CXTOUT; 10 to 33pF

4 MHz

XOUT

(4) 6 MHz (for OSD) LC Resonator

TBEKSES-30361FBY (TOKO)

Note: An electrical shield by metal shield plate on the surface of the IC package should be recommendable in order to prevent the device from the high electric fieldstress applied from CRT (Cathode Ray Tube) for continuous reliable operation.

# **Typical Characteristics**