# PLL TV MICROCOMPUTER INTERFACE

- HIGHLY INTEGRATED SOLUTION INCLUD-ING PLL SYNTHESIZER, NV MEMORY, D/A CONVERTERS, BAND SELECT OUTPUTS, CLOCK OSCILLATOR, IR SIGNAL PRE-PRO-CESSOR AND SERIAL BUS INTERFACE

- 32 x 16 BITS OF NV MEMORY WITH LIFE-TIMES OF 10<sup>4</sup> CYCLES/WORD AND MINIMUM 10 YEARS RETENTION STORES TUNING DATA FOR 30 CHANNELS PLUS PRESET VALUES FOR THE SIX ANALOG OUTPUTS

- PRE-PROCESSOR FOR INFRARED REMOTE CONTROL SIGNALS REDUCES COMPO-NENT COUNT

- SIX PWM D/A CONVERTERS WITH 64-STEP RESOLUTION

- FOUR OPEN-DRAIN BAND SELECT OUT-PUTS RATED TO 13.2 V

- ON-CHIP 4 MHz CLOCK OSCILLATOR WITH BUFFERED OUTPUT

- INTEGRATED DIGITAL POWER-ON RESET

- 3-WIRE SERIAL BUS TO LOAD/READ INTER-NAL REGISTERS

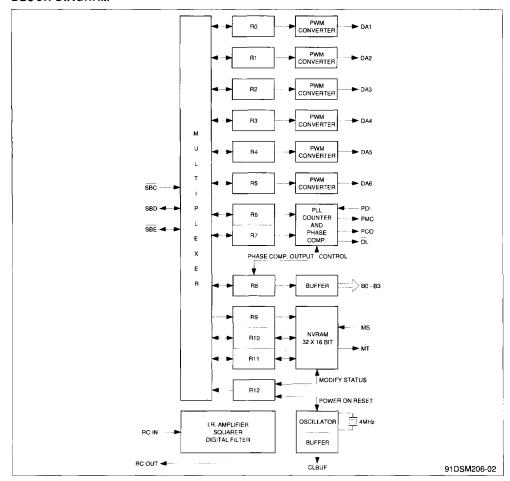

### DESCRIPTION

The M206 is a highly integrated, programmable LSI integrated circuit for microcomputer controlled TV applications, realized using an advanced N-channel double polysilicon gate technology (NVMOS) that allows the integration of non-volatile memory and standard logic on the same chip.

It contains a phase-locked loop (PLL) synthesizer, six pulse-width modulation (PWM) digital/analog converters, a four-bit parallel output buffer, clock oscillator with buffered output, pre-processor for infrared remote control signals and a 3-wire serial bus interface.

The M206 interfaces with a microcomputer through the three-wire serial bus and is programmed by loading thirteen internal registers - twelve of which are readable to simplify programming.

The PLL synthesizer requires an external 64 + 15/16 prescaler and divider and works with a phase comparator reference frequency of 0.9765 kHz. Outputs are provided to control the division ratio of the prescaler and to signal the out-of-lock condition to the microcomputer.

The infrared remote control signal pre-processor consists of a preamplifier, a squarer and a digital filter to separate noise from signals transmitted by the M708, M709 and M710 remote control transmitters. The output of this pre-processor is connected to the interrupt input of a microcomputer programmed to receive and decode the signal.

The M206 is supplied with two separate 5 V supply inputs, each provided with internal power-on reset circuits. The first,  $V_{DD1}$ , supplies the remote control and clock circuits in both standby and TV set operation. The second,  $V_{DD2}$ , supplies the rest of the circuits and is only active during TV operation.

The M206 is packaged in a 28-pin dual in-line plastic package.

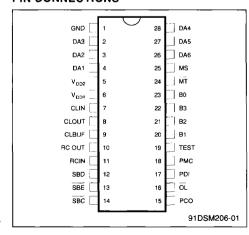

## PIN CONNECTIONS

#### PIN DESCRIPTION

**DA1-DA6 -** Digital/Analog converter outputs (opendrain outputs)

Output from the six pulse-width modulation D/A converters.

**B0-B3 -** Band drive outputs (open-drain outputs)

Outputs from the four-bit buffer used for band selection.

SBD - Serial Bus Data (bidirectional)

Data line for serial communication with a microcom-

Data line for serial communication with a microcomputer.

SBE - Serial Bus Enable (bidirectional, active low) Enables serial bus transmissions.

SBC - Serial Bus Clock (input, active low)

Clock for serial bus transmissions.

RCIN - Remote Control signal Input (analog input) Input to the infrared remote control signal preprocessor. Connected to the output of the IR preamplifier. Minimum input level 0.5 V peak-to-peak.

**RCOUT** - Remote Control signal Output

Output from the infrared remote control signal preprocessor. To be connected to the interrupt input of

a microcomputer.

**PDI** - Programmable Divider Input (input)

This pin is the input of the programmable divider and is connected to the output of the prescaler.

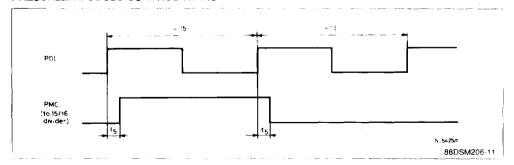

**PCM** - *Prescaler Modulo Control (output)*Control signal to set the prescaler division ratio (15 if high, 16 if low).

OL - Out of Lock (output. active low)

Signals an out of lock condition. This output is also active during the power on reset sequence.

PCO - Phase Comparator Output

The output of the phase comparator. Connected to the input of a low pass filter used to generate the tuning voltage.

TEST - Test pin (input)

The test pin is used only to test the device and is not specified for customer use. It must be connected to ground.

**CLIN, CLOUT -** Clock oscillator connections A 4 MHz quartz crystal is connected between these pins.

$V_{DD1}$ ,  $V_{DD2}$ , GND - Power Supply Connections  $V_{DD1}$  is the + 5 V standby supply input;  $V_{DD2}$  is the main + 5 V supply input.

MS - Memory Supply Input (input)

Programming pulses for the NV memory are supplied to this pin during store cycles.

MT - Memory Timing (output. active low)

This output supplies the timing for the memory write pulses supplied to the MS input during store cycles.

CLBUF - Clock Buffer (output)

This is a buffered output from the on-chip clock oscillator and can be used to drive other components (for example the microcomputer).

#### **BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

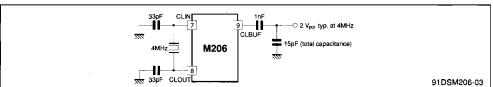

#### CLOCK

To use the internal oscillator a 4 MHz quartz crystal is connected between the pins CLIN and CLOUT. If an external clock is used this must be connected to CLIN and CLOUT left unconnected or, if required as

a clock output, loaded by a capacitor up to 15 pF. The minimum external clock amplitude is 2 V peak-to-peak. A buffered clock output, CLBUF, is provided which can drive up to three  $\pm$  100  $\mu\text{A}$  loads.

## LOADING AND READING INTERNAL REGISTERS

The M206 is programmed by loading a set of internal registers through a 3-wire serial bus. The functions of these registers are summarised in table 1.

**TABLE 1: Summary of Internal Registers**

| Register |    | Address |    |    | Number of | Function                                  |  |  |

|----------|----|---------|----|----|-----------|-------------------------------------------|--|--|

| Number   | А3 | A2      | A1 | A0 | Bits      | Pulction                                  |  |  |

| 0        | L  | L       | L  | L  | 6         | D/A Converter n° 1                        |  |  |

| 1        | L  | L       | L  | Н  | 6         | D/A Converter nº 2                        |  |  |

| 2        | L  | L       | н  | L  | 6         | D/A Converter nº 3                        |  |  |

| 3        | L  | L       | Н  | н  | 6         | D/A Converter n° 4                        |  |  |

| 4        | L  | Н       | L  | L  | 6         | D/A Converter nº 5                        |  |  |

| 5        | L  | Н       | L  | Н  | 6         | D/A Converter n° 6                        |  |  |

| 6        | L  | Н       | Н  | L  | 7         | PLL Counter (MSB)                         |  |  |

| 7        | L  | Н       | Н  | Н  | 8         | PLL Counter (LSB)                         |  |  |

| 8        | Н  | L       | L  | L  | 7         | Buffer Outputs/Phase Comp. Output Control |  |  |

| 9        | Н  | L       | L  | Н  | 5         | NV Memory Address                         |  |  |

| 10       | Н  | L       | Н  | Н  | 8         | NV Memory DATA                            |  |  |

| 11       | Н  | L       | Н  | Н  | 8         | NV Memory DATA                            |  |  |

| 12       | Н  | Н       | L  | L  | 2         | NV Memory Modify Control/Reset Control    |  |  |

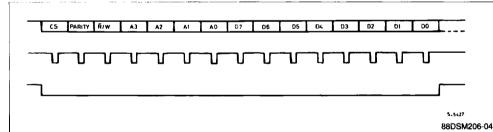

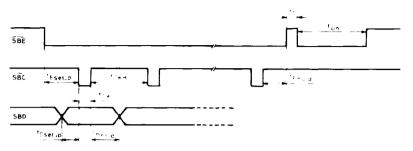

The 3-wire serial <u>bus</u> consists of the signals <u>SBD</u> (Serial Bus Data), <u>SBE</u> (Serial Bus Enable) and <u>SBC</u> (Serial <u>Bus</u> Clock). The enable and data pins, <u>SBD</u> and <u>SBE</u>, are bidirectional.

Data is accepted when the clock is low (active) and latched into the M206 on the low-high transition of the clock. All bus transfers are controlled by SBE.

REGISTER LOADING. Serial data transferred from the microprocessor to the M206 has the following format

| Bit    | +Description                                               |  |  |  |  |  |

|--------|------------------------------------------------------------|--|--|--|--|--|

| cs     | Chip Select (always low)                                   |  |  |  |  |  |

| PARITY | Parity bit (the number of " H " bits transmitted is odd)   |  |  |  |  |  |

| R/W    | Read/Write. High for Register Load ; Low for Register Read |  |  |  |  |  |

| A0-A3  | Register Address (see table 1)                             |  |  |  |  |  |

| D0-D7  | Data to be loaded into register (load operation only)      |  |  |  |  |  |

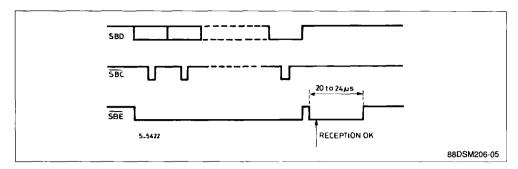

The received data word is checked - length, CS and parity - immediately after the low-high transition of SBE. If the received word is valid this is signalled to

the microprocessor by forcing the SBE line low fo  $20-24\mu s$ .

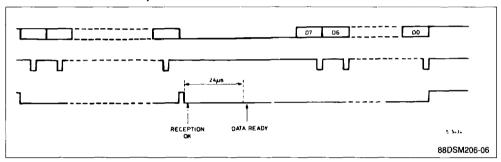

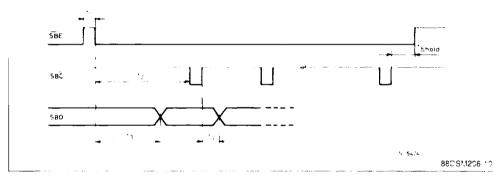

REGISTER READING. M206 registers are read by transmitting a 15 bit word as shown in fig. 4 with  $\overline{R}/W$  low and the address of the register to be read in A0, A1, A2, A3. Bits D0-D7 can be high or low except when register 9 is addressed.

If this word is received correctly the SBE line is im-

mediately pulled low by the M206 and after 24  $\mu$ s the contents of the addressed register will be available to be read. The microprocessor reads this data by sending eight clock pulses. Data is output on the low-high transition of SBC and the first data bit is available before the first clock pulse.

LOADING THE NON-VOLATILE MEMORY. Data is stored in the 32 x 16-bit NV memory by loading the new contents into registers 10 and 11 then the address into register 9. The memory modify cycle begins when the address has been loaded and successful completion is indicated by a logic "1" in bit zero of register 12.

The time for a modify cycle varies from a few milliseconds to several hundred milliseconds during the device lifetime and is not internally limited. The storage operation should be aborted after one second if it proves unsuccessful. This is done by setting bit zero of register 12.

READING THE NON-VOLATILE MEMORY. The NV memory is read by loading the address into register 9. The contents of the addressed word are automatically loaded into registers 10 and 11 and can be read by two register read operations. The data is ready 200 µs after the address load.

#### PLL COUNTER

The PLL counter consists of a single counter that acts as the program counter (11 bit) and is swallow counter (4 bit) alternately. Data for the PLL counter is loaded into registers 6 and 7. Register 6 must be loaded first because the register 7 load operation initiates the data transfer to the PLL counter.

The reference frequency is produced by dividing the clock frequency by 4096. With a 4 MHz clock this gives a reference frequency of 976.5 Hz.

An out-of-lock signal is generated (output OL) when the phase error between the reference frequency and the input frequency exceeds 0.72  $(2 \mu s)$ .

The phase comparator output, PCO, has a three-state push pull configuration with a high level of 5 V and a low level of 0 V (with zero current sink or pump). The output impedance (both states) is typically 200  $\Omega$  (400  $\Omega$  maximum). The phase comparator output can be set to a high impedance state (both

sink and pump transistors off) by setting bit 4 of register 8. The output is held in the high impedance state until this bit is reset. The phase comparator output should be set to high impedance when changing band.

RECOVERING LOCK. The phase comparator output can also be set to high and low levels to restore normal operation when the oscillator stops or the prescaler functions incorrectly at high frequency.

In the first condition (oscillator off) the prescaler sometimes oscillates, at high frequency. The loop reacts by reducing the varicap voltage in an attempt to reduce the frequency, thus worsening the situation. This out-of-lock <u>con</u>dition is signalled to the microprocessor (by the OL output) which can set the phase comparator output to low level, forcing the varicap voltage up and restarting the oscillator. The phase comparator output is forced low by setting bit 5 of register 8. After about 1 ms this bit is automatically reset and the loop should lock again.

When the out-of-lock condition is caused by a failure of the prescaler to operate correctly at high frequencies the loop reacts by increasing the voltage, hence the frequency, again worsening the situation. To recover from this condition the phase comparator output is set high. This is done by setting bit 6 of register 8 which, as in the previous case, resets itself after 1 ms.

The out-of-lock condition could also be caused by unwanted changes in band or PLL counter contents provoked by external interference (spikes on supply etc.). For this reason it is always advisable to reload the band and PLL counter registers before attempting to recover lock as described above. If the phase comparator output is in the high impedance state, the OL output signals the reset condition but not the out-of-lock condition.

## CALCULATING PLL COUNTER VALUES

- a) F = video carrier

- b) IF = 38.9 MHz

- c) The frequency to be synthesized is Fs = F + IF

- d) The Ref. frequency of the phase comparator is

$$F_{ref} = \frac{4.000MHz}{4096} = 0.97656kHz$$

e) Using the prescaler 64 + 15/16 the minimum frequency steps is

$$F_{ref} \times 64 = 62.5 \text{ kHz}$$

f) The modulo of division N is given by the ratio

between the frequency to be synthesized and the reference frequency multiplied by 64. The result has to be rounded.

$$NS = Integer rounded \left[ \frac{F_S}{F_{ref} \cdot 64} \right]$$

g) With the 64 + 15/16 prescaler and the particular counter of the M206 the division by N is given by

$$N_S = (I_S + 1) \cdot 15 + (R_S + 1) \cdot 16$$

where I (integer part) controls the division by 15 (program counter) and R (rest) controls the division by 16 (swallow counter). For ease of calculation we decrement  $N_S$  by one getting  $N_C = N_S - 1$ .

The numbers Ic and Rc are given by :

$$N_C = (I_C + 1) \cdot 15 + (R_C + 1) \cdot 16$$

$N_C - 31 = I_C \cdot 15 + R_C \cdot 16$

using the formulas:

$$R_C = N_C - 31 - 15 \cdot Integer \left[ \frac{N_C - 31}{15} \right]$$

$$IC = \frac{N_C-31-R_C\cdot 16}{15}$$

$$R_S = R_C + 1$$

$$I_S = I_C - 1$$

### Example:

Channel 21, F = 471.25 MHz

$$F_S = F + IF$$

,  $F_S = 471.25 + 38.9 = 510.15 MHz$

$$N_S = Integer rounded \left[ \frac{510.15 \cdot 10^6}{62.5 \cdot 10^3} \right]$$

$$N_C = N_S - 1 = 8161$$

R<sub>C</sub> = N<sub>C</sub> - 31 - 15 · Integer

$$\left[\frac{N_C - 31}{15}\right]$$

= 8161 - 31 - 15 · Integer  $\left[\frac{8161 - 31}{15}\right]$

$$I_C = \frac{N_C - 31 - R_C \cdot 16}{15} = \frac{8161 - 31}{15} = 542$$

$$R_S = R_C + 1 = 0 + 1 = 1$$

$$I_S = I_C - 1 = 542 - 1 = 541$$

R and I have to be translated into binary code.

#### DIGITAL/ANALOG CONVERTERS

The six pulse-width modulation (PWM) D/A converters have a resolution of 64 steps and an output frequency of 16 kHz (with 4 MHz clock). At power on reset they are set to a duty cycle of zero.

#### POWER ON RESET

The  $V_{DD1}$  and  $V_{DD2}$  supplies have an integrated digital power on reset with a duration of 250 ms.

The reset condition is signalled by a low level on the out-of-lock output, OL. The microprocessor can test this condition by reading bit 1 of register 12. This bit is zero during power on reset and the OL output remains active until it is read. Reading this bit automatically restores it to a high state.

During power on reset time commands from the micoprocessor are not acknowledged. Power on reset also sets the phase comparator output to a high impedance, state. It is restored by resetting bit 4 of register 8

### REMOTE CONTROL SIGNAL PRE-PROCESSOR

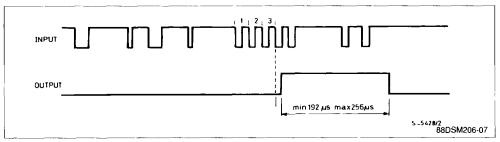

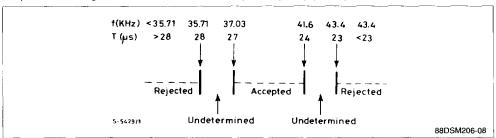

This section contains a preamplifier, squarer, digital filter and a pulse generator. The digital filter enables the pulse generator only if three successive negative going pulses (4 edges) are detected. The distance between these pulses must be in the range 24-27  $\mu s$  (about 37-41 kHz with a 4 MHz clock). The input is not tested for the duration of the output pulse (192-256  $\mu s$ ).

If this pre-processor is used in conjunction with M709 or M710 remote control transmitters valid signals can be recognized in the presence of extreme noise conditions. Separating the signals from the noise externally in this way reduces the number of interrupts that the microcomputer has to handle thus allowing it to concentrate on other takes. To take advantage of this section the M708, 709, 710 transmitters must operate with a clock frequency in the range 492-508 kHz.

The input can be DC or AC compled to the I.R. preamplifier.

In case of DC coupling the quiescent input level is suggested to be 1.5 V.

Response of the Digital Filter as a Function of the Input Frequency (in kHz).

|                                                                               | Convertors    | 1-6             | Regis              | ster 6 – PLL Pr               | ogram Counte      | er.            |

|-------------------------------------------------------------------------------|---------------|-----------------|--------------------|-------------------------------|-------------------|----------------|

| 5                                                                             | 0             |                 | 6                  |                               | 0                 |                |

| BINARY CODED R0-R5<br>ANALOG VALUE 6 bits                                     |               |                 |                    | PROGRAM COUNT<br>UPPER 7 BITS |                   |                |

| MSB                                                                           | LSB           |                 | MSB                |                               |                   | ]              |

| Register 7 – PLL P                                                            | rogram 'Swall | ow Counter.     |                    |                               |                   |                |

| 7                                                                             | -             | 0               |                    |                               |                   |                |

| PROGR. COUNT<br>LOWER 4 BITS                                                  | SWALI         |                 | ts                 |                               |                   |                |

| L                                                                             | SB MSB        | LSB             |                    |                               |                   |                |

| Register 8 – Band                                                             | Drive Outputs | :/Phase Comr    | parator Output (   | Control.                      |                   |                |

| 6                                                                             | omo output    |                 | a.a.o. output      | 001111011                     |                   |                |

|                                                                               |               |                 | T                  | T                             |                   |                |

| PCCH                                                                          | PCOL          | PCOZ            | B3                 | B2                            | B1                | В0             |

| PCOH +PCOL                                                                    | +PCOZ         | parator Outpu   |                    | e Comparator C                | Output            |                |

| L L                                                                           |               | ormal PLL Ope   |                    | e Comparator C                | output            |                |

|                                                                               |               | igh Impedance   |                    |                               |                   |                |

| L H                                                                           | LIL           | ow for 1 ms the | n returns automa   | atically to normal            | PLL operation.    |                |

| L H                                                                           | H L           | ow for 1 ms the | n returns to high  | impedance state               | Э.                |                |

| H L                                                                           |               |                 | en returns to norr |                               | n.                |                |

| H L                                                                           |               | ĭ               | en returns to high | impedance.                    |                   |                |

| Н Н                                                                           |               | ormal Operatio  |                    |                               |                   |                |

|                                                                               |               | igh Impedance   |                    | ally recet low after          | 1 me              | x              |

| H H                                                                           |               | and FOOL, FO    | On are automatica  | any reset low anter           | 1 1115.           |                |

| * These combinations                                                          | ,             |                 |                    |                               |                   |                |

|                                                                               |               | SS.             |                    |                               |                   |                |

| * These combinations                                                          |               | SS.             |                    |                               |                   |                |

| These combinations  Register 9 – NV M                                         | emory Addres  | SS.             |                    |                               |                   |                |

| * These combinations  Register 9 – NV Mi 4                                    | emory Addres  | 5S.             |                    |                               |                   |                |

| * These combinations  Register 9 – NV M  4  ADDRESS  MSB                      | o 5 bits      |                 |                    |                               |                   |                |

| * These combinations Register 9 – NV Mi 4  ADDRESS                            | o 5 bits      |                 | . 7                |                               |                   | 0              |

| * These combinations  Register 9 – NV Med  ADDRESS  MSB  Registers 10 & 11  7 | o 5 bits      | √ Data.         | )                  |                               | R EIGHT<br>A BITS | 0<br>R1<br>8 t |

SGS-THOMSON MICROELECTRONICS

8/14 136 1

0

| Flag          | L                   | н                  |        |

|---------------|---------------------|--------------------|--------|

| MODIFY STATUS | Modify in progress. | Modify over.       | TAB 04 |

| RESET STATUS  | Reset actived.      | Reset not actived. |        |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                              | Parameter                                                                                                | Value                     | Unit     |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|----------|--|

| V <sub>DD1</sub> , V <sub>DD2</sub> | Supply Voltage                                                                                           | - 0.3 to 7                | ٧        |  |

| V <sub>PP</sub>                     | Memory Supply Voltage                                                                                    | - 0.3 to 28               | ٧        |  |

| Vı                                  | Input Voltage (except Pin 11)<br>Pin 11                                                                  | - 0.3 to 7<br>- 0.3 to 15 | V        |  |

| V <sub>O (off)</sub>                | Off State Output Voltage (except Pins 2-3-4-26-27-28-20-21-22-23-24) Pins 2-3-4-20 to 23-26 to 28 Pin 24 | 7<br>15<br>28             | V        |  |

| loL                                 | Output Current (except Pins 2–3–4–26–27–28)<br>Pins 2–3–4–26–27–28                                       | 5<br>10                   | mA<br>mA |  |

| Іон                                 | Output Current (Pins 15, 9)                                                                              | - 5                       | mA       |  |

| P <sub>tot</sub>                    | Total Package Power Dissipation                                                                          | 1                         | W        |  |

| T <sub>stg</sub>                    | Storage Temperature Range                                                                                | - 25 to 125               | °C       |  |

| Toper                               | Operating Temperature Range                                                                              | 0 to 70                   | °C       |  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# STATIC ELECTRICAL CHARACTERISTICS (Tamb = 0 to 70°C; typical values are at Tamb = 25°C)

| Symbol              | Parameter             | Pins                             | Test Conditions                                           | Min. | Typ. | Max. | Unit |

|---------------------|-----------------------|----------------------------------|-----------------------------------------------------------|------|------|------|------|

| $V_{DD1},\ V_{DD2}$ | Supply Voltage        | 5–6                              |                                                           | 4.75 | 5    | 5.25 | ٧    |

| V <sub>PP</sub>     | Memory Supply Voltage | 25                               |                                                           | 24   | 25   | 26   | ٧    |

| VIL                 | Input Low Voltage     | 12-13-14-17                      |                                                           | 0    |      | 0.8  | ٧    |

| ViH                 | Input High Voltage    | 12-13-14-17                      |                                                           | 2.4  |      | 5.25 | ٧    |

| V <sub>IPP</sub>    | Peak to Peak Signal   | 11                               | AC COUPLING                                               | 0.5  |      | 13.2 | V    |

| V <sub>TH</sub>     | Threshold Voltage     | 11                               | DC COUPLING                                               |      | 1.25 |      | ٧    |

| VoL                 | Output Low Voltage    | 10-12-13<br>16-18-20<br>21-22-23 | V <sub>DD</sub> = 4.75 V<br>I <sub>OL</sub> ≈ 1.6 mA      |      |      | 0.4  | ٧    |

|                     |                       | 9                                | V <sub>DD</sub> = 4.75 V<br>I <sub>OL</sub> = 0.2 mA      |      | ,,,, | 0.4  | ٧    |

|                     |                       | 15                               | V <sub>DD</sub> = 4.75 V<br>I <sub>OL</sub> = 1 mA        |      | 0.2  | 0.4  | ٧    |

|                     |                       | 2-3-4-26<br>27-28                | $V_{DD} = 4.75 \text{ V}$ $I_{OL} = 5 \text{ mA}$         |      |      | 1    | ٧    |

|                     |                       | 24                               | $V_{DD} = 4.75 \text{ V}$ $I_{OL} \approx 2.5 \text{ mA}$ |      |      | 8    | V    |

B-06

## STATIC ELECTRICAL CHARACTERISTICS (continued)

| Symbol           | Parameter                        | Pins                                   | Test Conditions                                                                         | Min. | Тур.                   | Max.                           | Unit |

|------------------|----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------|------|------------------------|--------------------------------|------|

| VoH              | Output High Voltage              | 9–18                                   | $V_{DD} = 4.75 \text{ V}$<br>$I_{OH} = -0.2 \text{ mA}$                                 |      |                        | 2.4                            | ٧    |

|                  |                                  | 15                                     | I <sub>OH</sub> = -1 mA                                                                 |      | V <sub>DD2</sub> - 0.2 | V <sub>DD2</sub> 0.4           | ٧    |

| IO (off)         | Output Leakage Current           | 2-3-4-10-16<br>20-21-22-23<br>26-27-28 | V <sub>DD</sub> = 4.75 V<br>V <sub>O (off)</sub> = 5.25 V                               |      |                        | 10                             | μA   |

|                  |                                  | 24                                     | V <sub>DD</sub> = 4.75 V<br>V <sub>O (off)</sub> = 26 V                                 |      |                        | 100                            | μА   |

| I <sub>IL</sub>  | Input Low Current                | 12-13                                  | V <sub>DD</sub> = 5.25 V<br>V <sub>OL</sub> = 0.4 V                                     |      | 50                     | 200                            | μΑ   |

| loz              | High Impedance output<br>Current | 15                                     | $V_O = 0$ to $V_{DD2}$                                                                  |      | ± 20                   |                                | nA   |

| I <sub>DD1</sub> | Supply Current                   | 6                                      | V <sub>DD1</sub> = 5.25 V                                                               |      |                        | 8                              | mA   |

| I <sub>DD2</sub> | Supply Current                   | 5                                      | V <sub>DD2</sub> = 5.25 V                                                               |      |                        | 30                             | mA   |

| Ірр              | Memory Supply current            | 25                                     | V <sub>PP</sub> ≈ 26 V  ■ Write Peak Average  ■ Erase Peak Average  ■ Read Peak Average |      |                        | 40<br>11<br>7<br>4.5<br>6<br>2 | mA   |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

| Symbol               | Parameter                                        | Test Conditions | Min. | Tup. | Max. | Unit |

|----------------------|--------------------------------------------------|-----------------|------|------|------|------|

| tckL                 | SBC LOW Time                                     |                 | 2    |      | 50   |      |

| tckH                 | SBC HIGH Time                                    |                 | 4    |      |      | 1    |

| t <sub>E setup</sub> | SBE Set-up to SBC falling edge time              |                 | 0.5  | -    | !    | 1    |

| t <sub>E hold</sub>  | SBE Hold Time from SBC rising edge               |                 | 3    |      | ,    | Ï    |

| t <sub>D setup</sub> | Data Setup Time                                  |                 | 1    |      |      | 1    |

| t <sub>D hold</sub>  | Data Hold time                                   |                 | 1    |      |      | 1    |

| t <sub>1</sub>       | Time between SBE Rising Edge and OK of Reception |                 |      |      | 3    | μs   |

| tok                  | OK of Reception Time                             |                 |      | 22   | 26   | 1    |

| t <sub>2</sub>       | Minimum SBC Delay Time from OK of Reception      |                 | 26   |      |      | 1    |

| t <sub>3</sub>       | Data Valid Time from OK of Reception             |                 |      | 20   | 25   | 1    |

| t4                   | Data Valid Time from SBC Pulse                   |                 |      |      | 4    | 1    |

| t <sub>5</sub>       | Propagation Delay of PMC                         |                 |      |      | 0.9  | 1    |

## TIMING WAVEFORMS

## REGISTER LOAD

d1

88D\$M206-09

## REGISTER READ

## PRESCALER MODULO CONTROL TIMING

## INPUT AND OUTPUT CONFIGURATIONS

## **SBC**

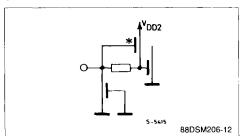

## PDI

## CLIN

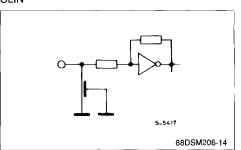

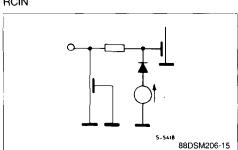

**RCIN**

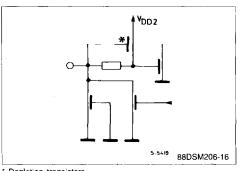

# SBD, SBE

DA1-DA6, B0-B3, OL, RCOUT

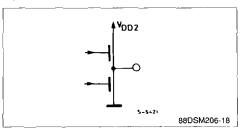

## **PCO**

PMC, CLOUT, CLBUF

12/14

140

<sup>\*</sup> Depletion transistors.

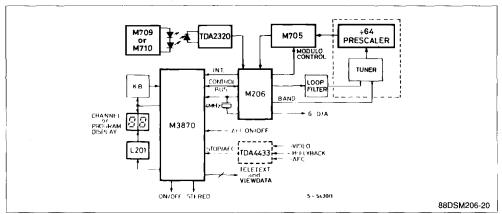

## TYPICAL APPLICATIONS

Remote Controlled TV Frequency Synthetizer.

- Remote Control Decoding by Microprocessor.

- 32 Station Non-Volatile Memory or 30 Station

- Memory + Normalized D/A Positions

- Flexible System Operation

- Frequency Synthesis of all Standard and CATV Channels

- Direct Channel Selection

- ± 4 MHz Fine Tuning (62.5 kHz per Step)

- Automatic Search within Channel (using TDA4433)

- \_ AFC Operation (using TDA4433)

- \_ 6 D/A Converters

- Teletext and Viewdata Data Bus Conversion

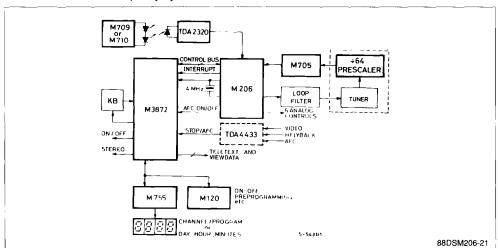

Remote Controlled TV Frequency Synthetizer and Clock Timer.

Frequency Synthesis as described in the Basic Configuration with the addition of :

- Further Station Memory, using M120, 1 K NV MEMORY

- Clock and programmable timer for automatic switch ON/OFF, using M755.

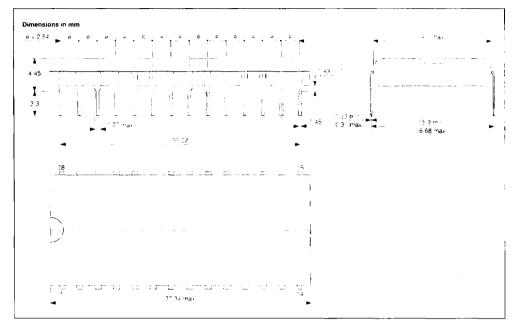

## **PACKAGE MECHANICAL DATA**

28 PINS - PLASTIC DIP