### MN187125

#### Features

- ROM capacity:12,288 x 8 bits

- RAM capacity:320 X 8 bits(data area and stack area)

- Machine cycle:0.475 μs(at 8.38 MHz),122 μs(at 32 kHz)

Soft programmable

• Interrupt:External interrupt 2 levels

(one of them with noise filter)

Timer interrupt

4 levels

Serial interrupt 2 levels FLT(key scan)interrupt

1 level

ADT(RAM automatic transfer)interrupt

1 level

• Timer counter:

8-bit programmable timer x 3 with prescaler

Pulse width measuring function

Event count function

Timer output function

Time base counter x 1

For time base, watch

Watchdog timer x 1

• Serial interface:

8-bit synchronous type x 2

Upper compatible with MN1500 series

1-to 8-bit send/receive

Arbitrary bits send by the swap

mode(applied to remote control send)

Whether MSB/LSB is to be the first, and

clock polarity soft programmable

MNOS interface function

Start condition function

• Fluorescent display tube drive function:

Max.16 segments x 16 digits(max.26 in total)

Comonly available for key scan

Dimmer 16 steps

• PWM output:14-bit resolution(7-bit basic cycle + 7

-bit additional pulse)

Repeat cycle 15.6 ms(basic cycle 122

$\mu$ s)

• Analog input:4-bit simple A/D converter 3 channels

- Sync.signal detecting counter:Counts an input signal every constant cycle(measures a horizontal sync.signal)

- Buzzer output:2 kHx/4 kHz

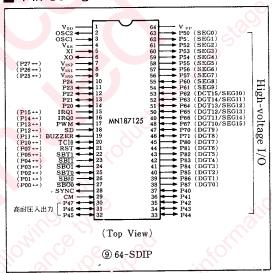

#### Pin Configuration

- Remote control recieve function:Reception by external interrupt input with noise filter

- ADT function: Capable of transferring up to 255byte data in the RAM space. Transfer enabled among 3 addresses.

- Standby mode:STOP/HALT mode

Totally 9 modes available in combination with clock selection(NORMAL/IDEL/SLOW mode)

• Operating voltage range:

4.5 to 5.5 V(at 8.38 MHz)

2.7 to 5.5 V(at 32 kHz,STOP)

• I/O pins: 5 for general purpose I/O

18 for high-voltage I/O

(fluorescent display tube output)

16 for high-voltage output

(fluorescent display tube output)

16 for combined I/O(commonly used for interrupt input, serial interface)

- Package:64-SDIP

- Piggyback:EP187324

- Process:Silicon gate CMOS

### 8-Bit 1-Chip Microcomputers

#### ■ Pin Descriptions

| Symbol                            | Pin Name                                              | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|-------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{	extsf{DD}} \ V_{	extsf{ss}}$ | Power supply                                          | I        | Connect $+5V\pm10\%$ to $+3V\pm10\%$ to $V_{DD}$ , and 0 V to $V_{SS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{\mathtt{PP}}$                 | High-voltage out-<br>put pull-down volt-<br>age input | I        | Connect a voltage supplied to the pull-down resistors of the Ports 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC1<br>OSC2                      | Clock input<br>Clock output                           | O        | Oscillation pins to connect $f_{osc}$ ceramic oscillatior or cristal oscillator. When inputting a clock from the external, input to OSC1 and open the OSC2 pin. They are not available in the external clock mode when the STOP or SLOW mode is used.                                                                                                                                                                                                                                                                 |

| XO                                | Clock input<br>Clock output                           | O        | Oscillation pins to connect $f_x$ ceramic oscillator or crystal oscillator. When inputting a clock from the external, input to XI and open the XO pin. They are not available in the external clock mode when the STOP mode is used.                                                                                                                                                                                                                                                                                  |

| SYNC                              | Timing output                                         | 0        | Output a clock of $f_{\rm osc}/32768$ . Available for watch setting standard clock.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CM                                | Chip mode selector                                    | I        | Connect to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RST                               | Reset input<br>(Port 07)<br>(Schmidt)                 | I/O      | Pin to reset at power-on time. It is assigned to the port 07 and incorporated a pull-up resistor(typ. 50 k $\Omega$ ). When reset is cancelled,there automatically occurs a hardware wait for system clock oscillation to be stabilized. The low level is outputted by writing "0" to the Port 07, when reset is applied by software as well. An output type is N-channel open drain. When inserting a capacitor between $\overline{RST}$ and $V_{DD}$ , it is recommended to connect a discharge diode between them. |

| P00~P05<br>P07                    | Special port P0                                       | I/O      | 7-bit I/O/input ports with special functions. Input/output can be set for each bit by the I/O direction register P0DIR. For details of each pin, see RST, SBO0, SBO1, SBI0, SBI1, SBT0 and SBT1. All the pins are placed in the input mode at reset time.                                                                                                                                                                                                                                                             |

| P10~P15                           | Special port P1                                       | I/O<br>I | 6-bit I/Oinput ports with special functions. For P10 through P13, input/output can be set for each bit by the I/O direction register P1DIR. P14 and P15 are input only ports. For details of each pin, see TCI0, BUZZER, RMOUT, PWM, IRQ0, IRQ1, respectively. P10 through P13 are placed in the input mode at reset time.                                                                                                                                                                                            |

| P20~P23                           | I/O port P2                                           | I/O      | 4-bit CMOS 3-state I/O ports. Input/output can be set for each bit by the I/O direction register P3DIR. They are placed in the input mode at reset time. P20 is also available as a serial clock.                                                                                                                                                                                                                                                                                                                     |

| P24~P27                           | Special port P2                                       | I/O      | 4-bit CMOS 3-state I/O ports with special functions. Input/output can be set for each bit by the I/O direction register P3DIR. For details of each pin, see $V_{\text{REF}}$ , VINO, SD and $V_{\text{INI}}$ . All the pins are placed in the input mode at reset time.                                                                                                                                                                                                                                               |

## 8-Bit 1-Chip Microcomputers

### ■ Pin Descriptions(Continued)

| Symbol             | Pin Name                                                             | I/O | Description                                                                                                                                                                                                                                                                                                             |

|--------------------|----------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P40~P47            | High-voltage input<br>port P4                                        | I   | 4-bit high-voltage I/O ports. P40-P43 are input only, and P44-P47 are I/O pins.                                                                                                                                                                                                                                         |

| P50~P57<br>P80~P87 | High voltage output port P5,P8                                       | 0   | The ports P5 and P8 are high voltage output ports. An output type is P-channel open drain. Pull-down resistors are incorporated between these ports and the Vpp pin. They are set to the Low level at reset time.                                                                                                       |

| P60~P67<br>P70~P71 | High voltage I/O port P6, P7                                         | I/O | The port P6 is an 8-bit high voltage I/O port, and P7 is a 2-bit one. An output type is P-channel open drain, pull-down resistors are incorporated between these ports and the Vpp pin. They are set to the Low level at reset time. The pull-down resistor of P6 is detachable by a mask option.(bit by bit)           |

| SBO0<br>SBO1       | (Port 00)<br>(Port 03)<br>Serial interface<br>data output            | I/O | Serial interface send data output pin. An output type is CMOS push-pull or N-channel open drain. Which type is to be used is software programmaole. \$\overline{SBO0}\$ and \$\overline{SBO1}\$ are assigned to the port 00 and Port 03, respectively, and available as I/O pins when the serial interface is not used. |

| SBI0<br>SBI1       | (Port 01)<br>(Port 04)<br>Serial interface<br>data input             | I/O | Serial interface receive data input pins. An output type is CMOS 3-state. SBI0 and SBI1 are assigned to the Port 01 and Port 04, respectively and available as I/O pins when the serial interface is not used.                                                                                                          |

| SBT0<br>SBT1       | (Port 02)<br>(Port 05)<br>Serial interface<br>clock I/O<br>(Schmidt) | I/O | Serial interface send/receive clock I/O pins. An output type is CMOS 3-state. SBI0 and SBI1 are assigned to the Port 01 and Port 04, and available as I/O pins when the serial interface is not used.                                                                                                                   |

| TCIO               | Timer I/O (Port 10)                                                  | I/O | Clock output pin for the timer 1 and clock input pin for the timer 0. It serves as an output pin when the timer 1 is in the timer mode, and as an input pin when it is in the event count mode. An output type is CMOS 3-state. It is assigned to the Port 10 and available as an I/O pin when the timer 1 is not used. |

| BUZZER             | Buzzer<br>output<br>(Port 11)                                        | I/O | CMOS 3-state Output pin for $f_{\rm osc}/2^{10}$ or $f_{\rm osc}/2^{11}$ buzzer. Since it is assigned to the Port 11, it is available as a normal I/O pin when the buzzer is not used.                                                                                                                                  |

| RMOUT              | Pulse signal<br>output<br>(Port 12)                                  | I/O | Pulse signal output pin. Since it is assigned to the Port 12, it is available as a normal I/O pin when pulse output is not used.                                                                                                                                                                                        |

| PWM                | PWM output<br>(Port 13)                                              | I/O | 14-bit PWM CMOS 3-state output pin. Since it is assigned to the Port 13, it is available as a normal input pin when PWM is not used.                                                                                                                                                                                    |

### ■ Pin Descriptions (Continued)

| Symbol           | Pin Name                                                         | I/O | Description                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ0             | External interrupt input (port 14) (Schmidt) (Port 15) (Schmidt) | I   | External interrupt pin which receives an interrupt at a negative or positive edge. Which edge is to be made valid can be specified by the IRQM register. It is assigned to the Ports 14 and 15 and available as a normal input pin by masking an interrupt. IRQ1 incorporates a noise filter for receiving remote control. |

| $V_{\text{ino}}$ | (PORT24)                                                         | I/O | Reference voltage input pin for the comparator 0. Commonly used as the Port 24.                                                                                                                                                                                                                                            |

| $V_{\text{REF}}$ | (PORT25)                                                         | I/O | Comparison voltage input pin for the comparator 0. Commonly used as the Port 25.                                                                                                                                                                                                                                           |

| SD               | (PORT26)                                                         | I/O | Horizontal sync. signal input pin. Input from this pin is directly given to a 9-bit counter. Commonly used as the Port 26.                                                                                                                                                                                                 |

| $V_{\text{INI}}$ | (PORT27)                                                         | I/O | Comparison voltage input pin for the comparator 1. Commonly used as the Port 27.                                                                                                                                                                                                                                           |

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support

systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805