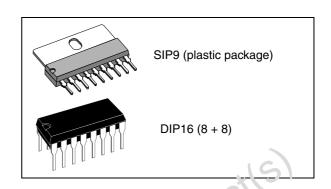

#### **STV8130AD**

# Adjustable and +3.3 V dual voltage regulator with disable and reset functions

#### **Features**

Input voltage range: 5 V to 18 VOutput currents up to 750 mA

■ Fixed precision output 1 voltage: 3.3 V ±2%

Adjustable output 2 voltage: 2.8 to 16 V

Output 1 with reset function

■ Output 2 with disable function by TTL Input

Short-circuit protection at both outputs

■ Thermal protection

■ Low dropout voltage

#### **Description**

The STV8130A# and STV8130AD are monolithic dual positive voltage regulators designed to provide a fixed precision output voltage of 3.3 V and an adjustable voltage between 2.8 and 16 V for currents up to 750 mA.

An internal reset circuit generates a reset pulse when the voltage of output 1 drops below the regulated voltage value.

Output 2 can be disabled via the T L input.

Short-circuit and thermal projections are included.

Table 1. Device summary

| Order code | Packaging |

|------------|-----------|

| STV8130A#  | Tray      |

| STV8130AD  | Tray      |

Contents STV8130AD

## **Contents**

| 1   | Description                              |

|-----|------------------------------------------|

| 2   | Electrical characteristics4              |

| 3   | Circuit description                      |

| 4   | Application diagrams8                    |

| 5   | Power dissipation and layout indications |

| 6   | Package mechanical data                  |

| 7   | Revision history                         |

| 005 | Description                              |

**STV8130AD Description**

#### **Description** 1

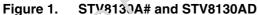

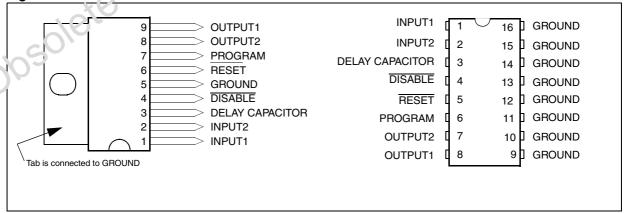

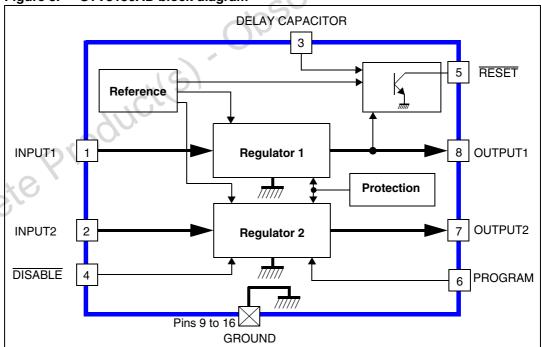

Figure 2. STV8130A# block diagram

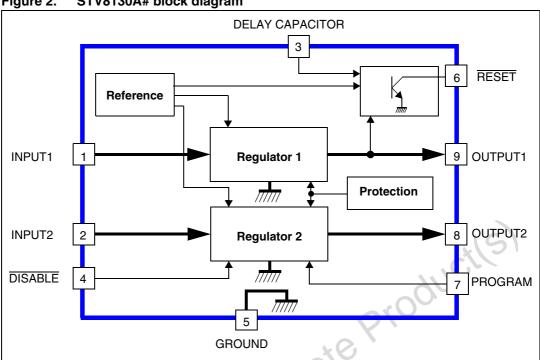

Figure 3. STV8130AD block diagram

Electrical characteristics STV8130AD

## 2 Electrical characteristics

Table 2. Absolute maximum ratings

| Symbol              | Parameter                                  | Value              | Unit |

|---------------------|--------------------------------------------|--------------------|------|

| V <sub>IN</sub>     | DC input voltage at pins INPUT1 and INPUT2 | 20                 | V    |

| V <sub>DIS</sub>    | Disable input voltage at pin DISABLE       | 20                 | V    |

| V <sub>RST</sub>    | Output voltage at pin RESET                | 20                 | V    |

| I <sub>OUT1,2</sub> | Output currents                            | Internally limited |      |

| Pt                  | Power dissipation                          | Internally limited |      |

| T <sub>STG</sub>    | Storage temperature                        | -65 to +150        | °C   |

| T <sub>J</sub>      | Junction temperature                       | 0 to +150          | °C   |

Table 3. Thermal data

| Symbol            | Parameter                                               | Value                  | Unit    |      |

|-------------------|---------------------------------------------------------|------------------------|---------|------|

| R <sub>thJC</sub> | Thermal resistance (junction-to-case)                   | STV8130A#<br>STV8130AD | 9<br>15 | °C/W |

| R <sub>thJA</sub> | Thermal resistance <sup>(1)</sup> (junction-to-ambient) | 50<br>56               | °C/W    |      |

| T <sub>J</sub>    | Maximum recommended junction temperature                | 140                    | °C      |      |

| T <sub>OPER</sub> | Operating free air temperature range                    | 0 to +70               | °C      |      |

<sup>1.</sup> Mounted on board. For more information, refer to Section 5.

Table 4. Electrical characteristics

| Symbol              | Parameter                              | Test conditions                                                                                 | Min.    | Тур.     | Max.       | Unit |

|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|---------|----------|------------|------|

| V <sub>OUT1</sub>   | Output voltage                         | I <sub>OUT1</sub> = 10 mA                                                                       | 3.23    | 3.30     | 3.37       | ٧    |

| V <sub>OUT2</sub>   | Output voltage                         | I <sub>OUT2</sub> = 10 mA                                                                       | 2.8     |          | 16.0       | V    |

| $V_{IO1,2}$         | Dropout voltage                        | I <sub>OUT1,2</sub> = 750 mA                                                                    |         |          | 1.4        | V    |

| V <sub>O1,2LI</sub> | Line regulation                        | 6 V < V <sub>IN1</sub> < 12 V<br>12 V < V <sub>IN2</sub> < 18 V<br>I <sub>OUT1,2</sub> = 200 mA |         |          | 50<br>100  | mV   |

| V <sub>O1,2LO</sub> | Load regulation                        | 5 mA < I <sub>OUT1</sub> < 600 mA<br>5 mA < I <sub>OUT2</sub> < 600 mA                          |         |          | 100<br>200 | mV   |

| IQ                  | Quiescent current                      | I <sub>OUT1</sub> = 10 mA, OUTPUT2<br>Disabled                                                  |         |          | 2          | mA   |

| V <sub>O1RST</sub>  | Reset threshold voltage <sup>(1)</sup> | $K = V_{OUT1}, I_{OUT1} \ge 50 \text{ mA}$                                                      | K - 0.4 | K - 0.25 | K - 0.1    | ٧    |

| $V_{RTH}$           | Reset threshold hysteresis             | See circuit description                                                                         | 20      | 50       | 75         | mV   |

| t <sub>RD</sub>     | Reset pulse delay                      | C <sub>e</sub> = 100 nF<br>See circuit description                                              |         | 25       |            | ms   |

Table 4. Electrical characteristics (continued)

| Symbol                | Parameter                               | Test conditions                                                                                      | Min. | Тур. | Max.       | Unit   |

|-----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------|------|------|------------|--------|

| V <sub>RL</sub>       | Saturation voltage in reset condition   | I <sub>RESET</sub> = 5 mA                                                                            |      |      | 0.4        | V      |

| I <sub>RH</sub>       | Leakage current in normal condition     | V <sub>RESET</sub> = 10 V                                                                            |      |      | 10         | μΑ     |

| K <sub>OUT1, 2</sub>  | Output voltage thermal drift            | $K_0 = \frac{\Delta V_0 \cdot 10^6}{\Delta T \cdot V_0}$ $T_J = 0 \text{ to } + 125^{\circ}\text{C}$ |      | 100  |            | ppm/°C |

| I <sub>OUT1,2SC</sub> | Short circuit output current            | $V_{IN1} = 7 \text{ V}, V_{IN2} = 10 \text{ V}$<br>$V_{IN1,2} = 16 \text{ V}^{(2)}$                  |      |      | 1.6<br>1.0 | А      |

| V <sub>DISH</sub>     | Disable voltage when pin DISA active)   | ABLE is high (OUTPUT2                                                                                | 2    |      |            | V      |

| V <sub>DISL</sub>     | Disable voltage when pin DISA disabled) | ABLE is low (OUTPUT2                                                                                 |      |      | 0.8        | V      |

| I <sub>DIS</sub>      | Disable bias current                    | 0 V < V <sub>DIS</sub> < 7 V                                                                         | -100 |      | 2          | μΑ     |

| V <sub>REF</sub>      | Reference voltage at PROGRAM pin        |                                                                                                      |      | 2.44 | MO.        | V      |

| T <sub>JSD</sub>      | Junction temperature for therm          | nal shutdown                                                                                         |      | 145  |            | °C     |

This reset signal is activated by a decrease of V<sub>OUT1</sub> voltage which can be due to an overload of pin OUT1 or by a lack of Input Voltage (V<sub>IN1</sub>).

Note:  $T_{AMB} = 25^{\circ} C$ ,  $V_{IN1} = 7 V$ ,  $V_{IN2} = 10 V$ , unless otherwise specified.

<sup>2.</sup> The output short-circuit currents are tested one channel at time. During a short-circuit, a large consumption of power occurs, but the thermal protection circuit prevents any excessive temperatures. A safe permanent short-circuit protection is only guaranteed for input voltages up to 16 V.

Circuit description STV8130AD

#### 3 Circuit description

The STV8130A# and STV8130AD are dual-voltage regulators with reset and disable functions.

The two regulation parts are supplied from a single voltage reference circuit trimmed by zener zapping during EWS testing. Since the supply voltage of this voltage reference is connected to pin INPUT1 ( $V_{IN1}$ ), the second regulator will not work if pin INPUT1 is not supplied.

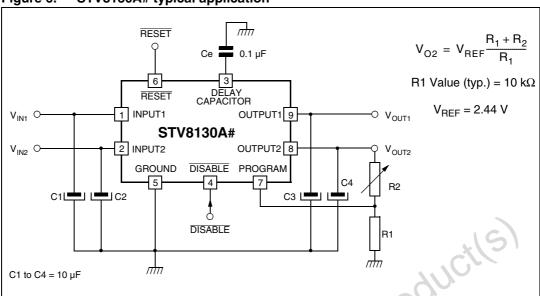

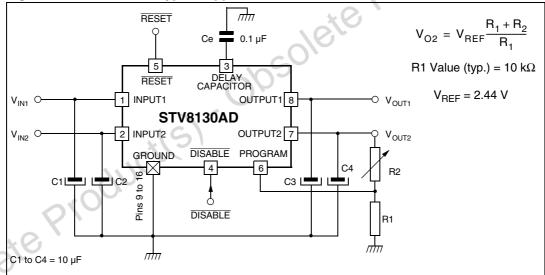

The adjustable voltage of pin OUTPUT2 ( $V_{OUT2}$ ) is defined by output bridge resistors (R1, R2): the values of these resistors are calculated to obtain, with the targetted value for  $V_{OUT2}$ , the reference voltage ( $V_{RFF} = 2.44 \text{ V}$ ) on the median point connected to pin PROGRAM.

The output stages are designed using a Darlington configuration with a typical dropout voltage of 1.2 V.

The disable circuit will switch off pin OUTPUT2 if a voltage less than 0.8 V is applied to pin DISABLE.

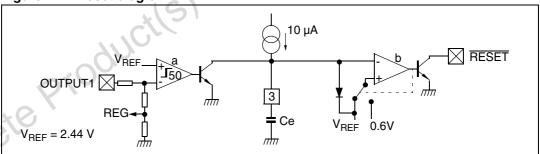

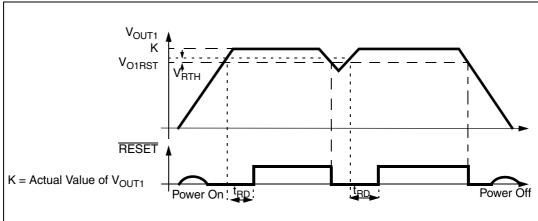

The reset circuit checks the voltage at pin OUTPUT1. If this voltage drops below  $V_{OUT1}$  - 0.25 V (3.05 V Typ.), the "a" comparator (*Figure 4*) rapidly discharges the external capacitor (Ce) and the reset output immediately switches to low. This drop can be caused by a parasitic loading condition on pin OUTPUT1 or by a too low value of  $V_{IN}$  (short powering off). When the voltage at pin OUTPUT1 exceeds  $V_{OUT1}$  - 0.2 V (3.1 V Typ.), the  $V_{Ce}$  voltage increases linearly to the reference voltage ( $V_{REF}$  = 2.44 V) corresponding to a reset pulse delay ( $t_{RD}$ ) as shown in *Figure 5*.

$$t_{RD} = \frac{C_e \times 2.44V}{10\mu A}$$

Afterwards, the reset output returns to high. To avoid glitches in the reset output, the second comparator "b" has a large hysteresis (1.84 V).

Figure 4. Reset diagram

STV8130AD Circuit description

Figure 5. Internal reset diagram

Obsolete Product(s). Obsolete Product(s)

## 4 Application diagrams

Figure 6. STV8130A# typical application

Figure 7. STV8130AD typical application

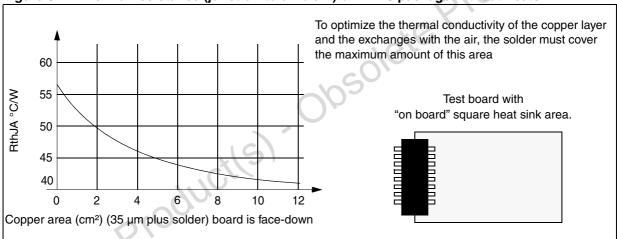

## 5 Power dissipation and layout indications

The power is mainly dissipated by the two device buffers. It can be calculated by the equation:

$$P = (V_{IN1}-V_{OUT1}) \times I_{OUT1} + (V_{IN2}-V_{OUT2}) \times I_{OUT2}$$

The following table lists the different R<sub>thJA</sub> values of these packages with or without a heat sink and the corresponding maximum power dissipation assuming:

- Maximum ambient temperature = 70° C

- Maximum Junction temperature = 140° C

Table 5. Power dissipation

| Device     | Heat sink | R <sub>thJA</sub> in °C/W | P <sub>MAX</sub> in W |

|------------|-----------|---------------------------|-----------------------|

| STV8130A#  | No        | 50                        | 1.4                   |

| 51V813UA#  | Yes       | 20                        | 3.5                   |

| STV8130AD  | No        | 56 to 40                  | 1.25 to 1.75          |

| 31 V0130AD | Yes       | 32                        | 2.2                   |

Figure 8. Thermal resistance (junction-to-ambient) of DIP16 package without heatsink

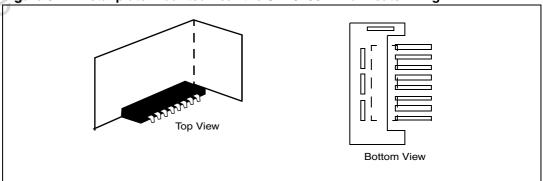

Figure 9. Metal plate mounted near the STV8130AD for heatsinking

# 6 Package mechanical data

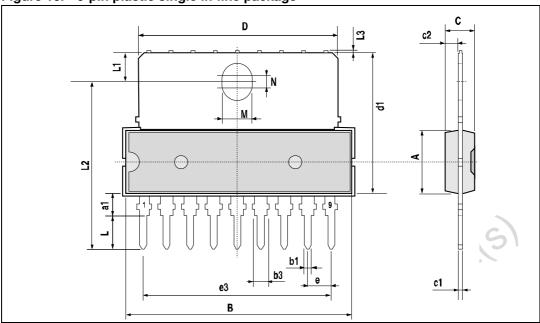

Figure 10. 9-pin plastic single in-line package

Table 6. 9-pin plastic single in-line package dimensions

|       | Dim.   |      | mm    |      | -0/e  | Inches |       |

|-------|--------|------|-------|------|-------|--------|-------|

|       | Dilli. | Min. | Тур.  | Max. | Min.  | Тур.   | Max.  |

|       | Α      |      |       | 7.1  |       |        | 0.280 |

|       | a1     | 2.7  | 16    | 3    | 0.106 |        | 0.118 |

|       | В      |      | 4/31  | 24.8 |       |        | 0.976 |

|       | b1     | 411  | 0.5   |      |       | 0.020  |       |

|       | b3     | 0.85 |       | 1.6  | 0.033 |        | 0.063 |

|       | С      |      | 3.3   |      |       | 0.130  |       |

|       | c1     |      | 0.43  |      |       | 0.017  |       |

| _\(   | c2     |      | 1.32  |      |       | 0.052  |       |

| , c0' | D      |      |       | 21.2 |       |        | 0.835 |

| 703   | d1     |      | 14.5  |      |       | 0.571  |       |

| 0     | е      |      | 2.54  |      |       | 0.100  |       |

|       | e3     |      | 20.32 |      |       | 0.800  |       |

|       | L      | 3.1  |       |      | 1.122 |        |       |

|       | L1     |      | 3     |      |       | 0.116  |       |

|       | L2     |      | 17.6  |      |       | 0.693  |       |

Table 6. 9-pin plastic single in-line package dimensions (continued)

| Dim.   | mm   |      |      | n Inche |       |       |

|--------|------|------|------|---------|-------|-------|

| Dilli. | Min. | Тур. | Max. | Min.    | Тур.  | Max.  |

| L3     |      |      | 0.25 |         |       | 0.010 |

| М      |      | 3.2  |      |         | 0.126 |       |

| N      |      | 1    |      |         | 0.039 |       |

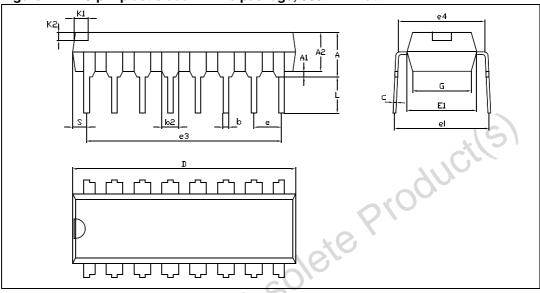

Figure 11. 16-pin plastic dual in-line package, 300-mil width

Table 7. 16-pin plastic dual in-line package dimensions

| Dim.   |       | mm    |       | Inches |       |       |

|--------|-------|-------|-------|--------|-------|-------|

| Dilli. | Min.  | Тур.  | Max.  | Min.   | Тур.  | Max.  |

| Α      |       | AUIO  | 5.33  |        |       | 0.210 |

| A1     | 0.38  | 0,    |       | 0.015  |       |       |

| A2     | 2.92  | 3.30  | 4.95  | 0.115  | 0.130 | 0.195 |

| b      | 0.36  |       | 0.56  | 0.014  |       | 0.022 |

| b2     | S     | 1.52  | 1.78  |        | 0.060 | 0.070 |

| c      | 0.20  | 0.25  | 0.36  | 0.008  | 0.010 | 0.014 |

| D      | 18.67 | 19.18 | 19.69 | 0.735  | 0.755 | 0.775 |

| е      |       | 2.54  |       |        | 0.100 |       |

| E1     | 6.10  | 6.35  | 7.11  | 0.240  | 0.250 | 0.280 |

| L      | 2.92  | 3.30  | 3.81  | 0.115  | 0.130 | 0.150 |

## 6.1 Environmentally-friendly packages

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance.

ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Obsolete Product(s). Obsolete Product(s)

STV8130AD Revision history

# 7 Revision history

Table 8. Document revision history

|        | Date               | Revision | Changes                                                                                                                           |

|--------|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

|        | August 2001        | 1.8      | General Update; DISABLE pin renamed DISABLE (function remains unchanged)                                                          |

|        | September<br>2001  | 1.9      | Thermal Data updated                                                                                                              |

|        | September<br>2001  | 2.0      | Addition of DIP16 package                                                                                                         |

|        | October 2001       | 2.1      | Thermal Data updated. Figure 2 and Figure 3 updated                                                                               |

|        | 31 January<br>2002 | 2.2      | Order code changed from STV8130A and STV8130D to STV8130A# and STV8130AD. Update of V <sub>O1RST</sub> values in <i>Section 2</i> |

|        | 05-Mar-2009        | 3        | Preliminary data banner removed, template updated and Section 6.1 added                                                           |

| Obsole | te Pro             | ducil    | Preliminary data banner removed, template updated and Section 6.1 added                                                           |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com