**TDA8380**

#### **GENERAL DESCRIPTION**

The TDA8380 is an integrated circuit intended for use as a control circuit in low-cost switched mode power supplies for television, monitors and small industrial equipment. The TDA8380 operates using duty factor regulation in the fixed frequency mode.

#### Features

- A low-current initialization circuit (maximum 150 μA) which can be switched off

- A bandgap reference generator

- Circuitry for slow-start combined with an accurate setting of the maximum duty factor (D<sub>max</sub>)

- Programmable low supply voltage protection with one default value

- High supply protection circuitry

- Error amplifier with a transfer characteristic generator (TCG)

- Protection against open- and short-circuited feedback loop

- An overload voltage foldback

- Primary current protection circuitry for both cycle-by-cycle and trip mode

- Protection against transformer saturation

- A direct drive output stage (sink current 2.5 A, source current 0.75 A)

- Anti-double pulse logic

- Protected against damage as a result of a short-circuited high-voltage transistor

- RC oscillator with synchronization input

#### QUICK REFERENCE DATA

| parameter                               | symbol           | min. | typ. | max. | unit |

|-----------------------------------------|------------------|------|------|------|------|

| Supply voltage                          | Vcc              | _    | 14   | _    | V    |

| Supply current                          | ¹cc              | _    | _    | 15   | mA   |

| Output pulse repetition frequency range | fo               | 10   | _    | 100  | kHz  |

| Operating ambient temperature range     | T <sub>amb</sub> | 25   | _    | + 70 | oC   |

## TDA8380

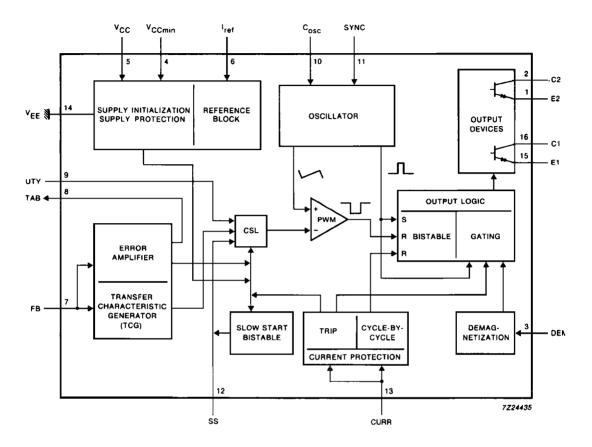

Fig.1 Block diagram.

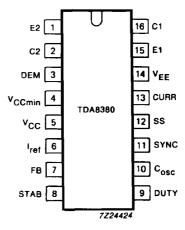

### **PINNING**

Fig.2 Pinning diagram.

| 1  | E2                 | Emitter of output source transistor                              |

|----|--------------------|------------------------------------------------------------------|

| 2  | C2                 | Collector of output source transistor                            |

| 3  | DEM                | Demagnetization sense input                                      |

| 4  | V <sub>CCmin</sub> | Minimum V <sub>CC</sub> threshold setting                        |

| 5  | $v_{CC}$           | Supply voltage                                                   |

| 6  | I <sub>ref</sub>   | Reference current setting                                        |

| 7  | FB                 | Feedback input                                                   |

| 8  | STAB               | Output error amplifier                                           |

| 9  | DUTY               | Pulse width modulator input                                      |

| 10 | $c_{OSC}$          | Oscillator capacitor                                             |

| 11 | SYNC               | Synchronization input                                            |

| 12 | SS                 | Maximum duty factor ( $D_{\mbox{max}}$ ) setting plus slow-start |

| 13 | CURR               | Input current protection                                         |

| 14 | $V_{EE}$           | Ground                                                           |

| 15 | E1                 | Emitter of output sink transistor                                |

| 16 | C1                 | Collector of output sink transistor                              |

|    |                    |                                                                  |

#### **FUNCTIONAL DESCRIPTION**

The TDA8380 is a control circuit which generates the pulses required to drive the switching transistor in a switched mode power supply (SMPS).

#### Supply

This device is intended to be used on the primary side of the power supply and can be supplied via a take-over (auxiliary) winding on the transformer.

The device is initialized via a high value resistor connected between the rectified mains voltage and the device's supply pin (pin 5), which causes the capacitor connected to this pin to charge slowly. When the voltage exceeds the initialization level (typically 17 V) the device will start up and the duty cycle will be slowly increased by the slow-start circuit. After a short period the take-over winding will supply the device. The value of the resistor is normally defined by the time taken to charge the capacitor. A one second delay between switching on and operation of the power supply is acceptable in most cases.

The operating voltage range is from 9 to 20 V. The supply pin is protected by a 23 V Zener diode. The supply protection circuit is activated once the Zener diode is conducting. The slow-start procedure begins after initialization, until then the output is off. The current drawn by the device during the initialization period is less than 150  $\mu$ A.

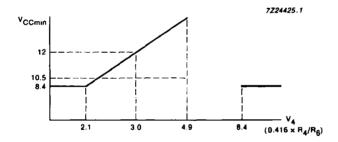

When the supply voltage falls below the minimum trip level, the device switches off and the start-up procedure is repeated. The minimum voltage supply threshold setting (V<sub>CCmin</sub>) can be set externally with a resistor connected between the V<sub>CCmin</sub> pin (pin 4) and ground (pin 14) (see Fig.3).

Fig.3 Trip level setting of minimum V<sub>CC</sub> protection level.

V<sub>CCmin</sub> can be set between 8.4 V (an internally fixed overriding protection level) and 17 V by means of an external resistor connected to pin 4.

When choosing the initialization and minimum supply voltages the following should be taken into account:

- The difference between the two voltages should be large enough to enable a supply voltage dip during start-up.

- The value of the minimum supply voltage should be high enough to ensure that the high-voltage transistor is correctly driven. A high protection level makes it possible to have a large resistor value in series with the base drive.

For battery line input operation, the V<sub>CCmin</sub> pin is connected to V<sub>CC</sub>, the start-up circuit is then inhibited and the device starts operating when V<sub>CC</sub> exceeds the 8.4 V protection level (this level has a hysteresis of approximately 50 mV). The device draws current continuously under these conditions.

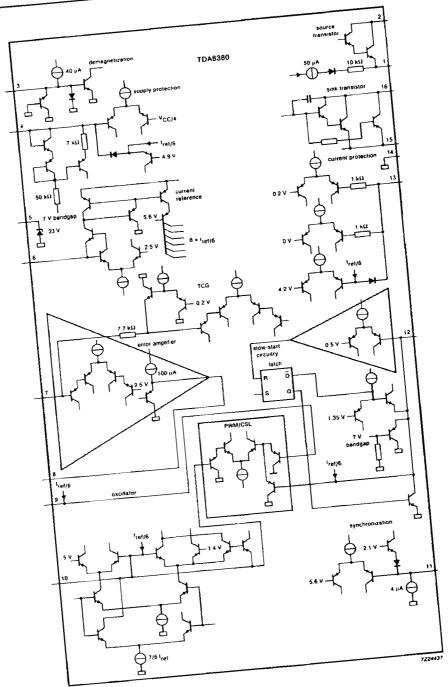

#### Reference block

A bandgap based reference generates a stabilized voltage of 7 V to supply most of the device's internal circuits, this decreases chip size and increases reliability. The only circuits connected to V<sub>CC</sub> are:

- The initialization circuit

- The output circuitry

- The series transistor of the stabilized voltage

By means of a resistor ( $R_6$ ) connected to the  $I_{ref}$  input a reference current is defined which determines six other device settings.

Part of the reference current is used to charge the oscillator capacitor ( $C_{10}$ ), therefore, the charging time is proportional to  $R_6 \times C_{10}$ . The maximum duty factor ( $D_{max}$ ) is set by the resistor connected to pin 12 ( $R_{12}$ ) and is defined by the ratio  $R_6/R_{12}$ . The minimum supply voltage (pin 5) set by the resistor ( $R_4$ ) at input  $V_{CCmin}$  is defined by:  $4/6 \times V_6 \times R_4/R_6$ .

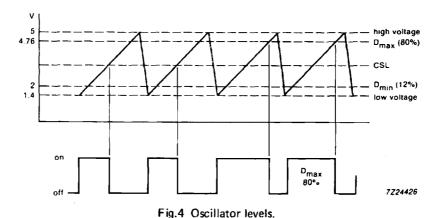

#### Oscillator

The oscillator capacitor is charged and discharged between the high and low voltage levels as defined by the bandgap reference (high voltage typically 5 V and low voltage typically 1.4 V). The charge current is 1/6 of the reference current, the discharge current having the same value as the reference current. The period is therefore defined by  $10 \times R_6 \times C_{10}$ .

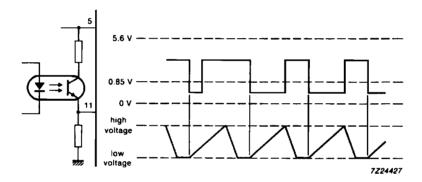

The oscillator flyback pulse is used to set the bistable in the output logic, however the output remains low until the positive ramp starts (see Fig.4). The oscillator can be synchronized by means of the SYNC pin. When this pin is connected to V<sub>CC</sub>, the oscillator is free running. When it is between 0.85 and 5.6 V, the oscillator stops at the low voltage level prior to the next positive ramp.

1124

#### FUNCTIONAL DESCRIPTION (continued)

#### Synchronization

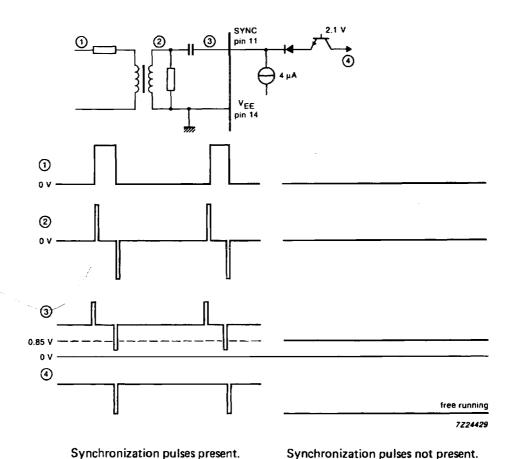

The synchronization input (pin 11) can be driven by either an optocoupler or a loosely coupled pulse transformer.

Figure 5(a) illustrates synchronization using the 0.85 V threshold and a digital signal connected to the SYNC input (for example, an optocoupler between pin 11 and V<sub>CC</sub>); the duty factor of the pulse is not very important. The oscillator starts at the first negative going edge of the sync. signal after the low voltage level has been reached. The synchronization frequency must be lower than the free running frequency. Synchronization must never affect the period time as this will corrupt the setting of the maximum duty factor.

Fig. 5(a) DC coupled synchronization using the 0.85 V level.

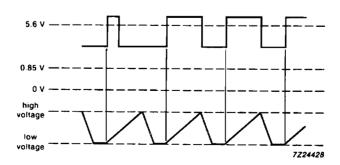

In Fig.5(b) the disabling threshold (5.6 V) is used for synchronization. In this case the oscillator starts at the positive going edge of the sync. signal.

Fig.5(b) DC coupled synchronization using the 5.6 V level.

Figure 6 illustrates synchronization using a pulse transformer. Internal circuitry causes a DC shift which informs the device that synchronization pulses are present (spikes around 0 V at the output of the pulse transformer) or not present (DC 0 V at the output of the pulse transformer). When synchronization is not used the SYNC pin must be connected to  $V_{CC}$ , it must not be connected directly to ground or left open.

Fig.6 Synchronization using a pulse transformer.

#### FUNCTIONAL DESCRIPTION (continued) Error amplifier

The error amplifier compares the feedback voltage of the SMPS with a reference voltage (nominally 2.5 V). The amplifier output at pin 8 enables gain setting. The amplifier is stable for a gain greater than 20 dB.

The output of the error amplifier is not internally connected to the Pulse Width Modulator (PWM). One input to the PWM is available at the DUTY input (pin 9) via the Control Slicing Level (CSL) circuit. Normally the STAB and DUTY pins are connected together, but direct driving of pin 9 via an optocoupler from the secondary side is also possible. A type of current mode control can be achieved by mixing the STAB signal with the primary current signal before applying it to the DUTY input.

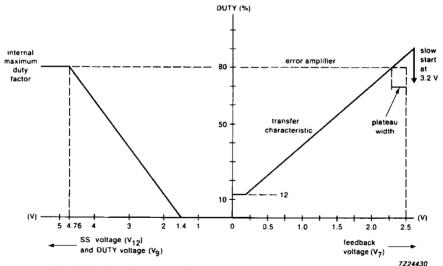

The feedback (FB) input (pin 7) is used as the input to the Transfer Characteristic Generator (TCG) circuit which ensures well defined duty factors at low FB voltages; a voltage foldback is an inherent characteristic. In Fig.7, the duty factor is shown as a function of the voltages at the FB, DUTY and SS inputs. The input which gives the lowest duty factor overrides the others.

The left hand curve is passed through during a slow-start (via the slow-start input pin 12) when the duty cycle slowly increases linearly with respect to  $V_{12}$ . The right-hand curve is passed through at start-up. The FB voltage slowly increases from zero and the duty factor, starting at 12%, increases until the maximum duty factor ( $D_{max}$ ) is reached. A few hundred millivolts later, the FB voltage reaches the start of the regulation curve which is at approximately 2.5 V. The plateau area between reaching  $D_{max}$  and starting the regulation curve is kept as small as possible (typically 200 mV).

Fig.7 The duty factor as a function of the FB, SS and DUTY voltages.

Due to the characteristics of the TCG, and the fact that an open FB input results in a low voltage at the FB input, open- and short-circuit feedback loops will result in low duty factors. When DC feedback is used across the error amplifier, the current capability of the error amplifier must be considered when determining the feedback resistor value.

When the input to the PWM (pin 9) is driven by an optocoupler, the TCG can be used when a rough primary voltage is applied to the FB input. In this situation an open feedback loop will cause an increase in the FB voltage as the duty factor rises to its maximum. As soon as the FB voltage exceeds the reference by 0.7 V, the slow-start is triggered.

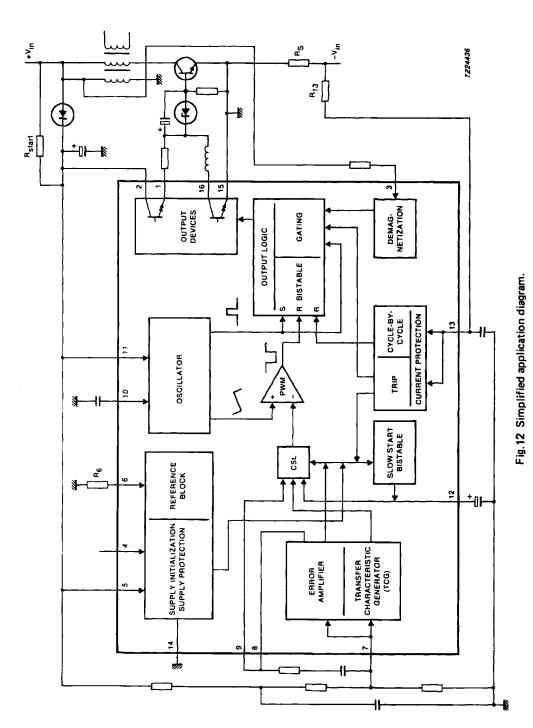

#### Demagnetization sense circuit

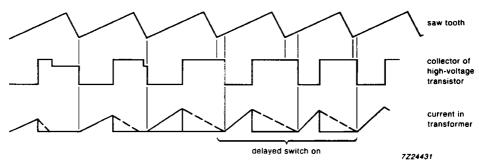

To enable the SMPS to be kept in the non-continuous mode, an input is available which delays switch-on of the high-voltage transistor until the transformer currents have decayed to zero. This is an effective way of avoiding transformer saturation. The waveforms illustrated by Fig.8 show demagnetization with respect to the application diagram of Fig.12.

Fig.8 Demagnetization function.

As long as the voltage of the take-over (auxiliary) winding (also used for supplying the device) is above  $0.6 \text{ V (V}_3)$  the output will be prevented from switching on.

#### Over-current protection

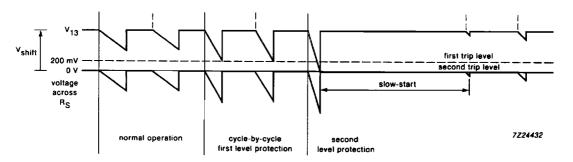

The over-current protection circuit (pin 13) senses the voltage across resistor  $R_s$  (see Fig. 12), which reflects the primary current. This generated voltage is negative-going as the emitter of the high-voltage power transistor is grounded (this circuit arrangement provides the IC with the best safeguard against a possible collector-emitter short-circuit in the power transistor). At pin 13, the negative voltage signal is shifted to a positive level by a voltage across resistor  $R_{13}$ . This voltage is set by the reference current at pin 13 and is defined by resistor  $R_6$  at the  $I_{ref}$  input (pin 6) and =  $1/6 \times V_{ref}/R_6$ . Therefore  $V_{shift}(V_{R13}) = V_{ref}/6 \times R_{13}/R_6$  or nominal 0.416 x  $R_{13}/R_6$  (V).

The positive current monitor voltage at pin 13 is compared with two voltage levels: the first level = 0.2 V and the second level = 0 V (see Fig.9).

The first trip level only switches off the high-voltage transistor for a cycle and puts the SMPS in a continuous cycle-by-cycle current protection mode.

The second trip level is only activated when the primary current rise is very fast which can occur during a short-circuited output. In this mode the high-voltage transistor is quickly switched off and the slow-start procedure is activated.

The difference between the first and second primary current peak levels is set by Rs:

$$I_2 - I_1 = 0.2/R_s$$

.

The absolute peak values are set by R6 and R13:

$$I_2 \times R_s = 0.416 \times R_{13}/R_6$$

or  $I_1 \times R_s = (0.416 \times R_{13}/R_6) - 0.2$

TDA8380

#### FUNCTIONAL DESCRIPTION (continued)

#### Over-current protection (continued)

Fig.9 Current protection.

#### Slow-start circuit

A slow-start occurs:

- At Switch-on of the SMPS

- After a current trip as described in the section Over-current protection

- After a low or high V<sub>CC</sub> trip.

The capacitor at the SS input is discharged and the slow-start bistable is reset when the voltage at the SS input falls below 0.5 V after which the circuit is ready for a slow-start. The dead time (during which the capacitor at the SS input is being charged to the 1.4 V lower level of the sawtooth) before duty cycle regulation starts is minimal. The SS input can also be used for  $D_{max}$  setting by connecting a resistor to ground. The voltage across this resistor is then limited to  $1/6 \times V_{ref} \times R_{12}/R_6$ .

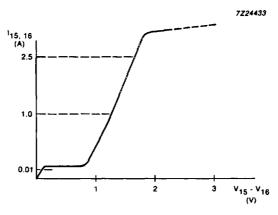

#### **Output stages**

The output stage consists of two NPN darlington transistors, their collector and emitter connected to separate pins (see Fig. 12). The top transistor is capable of sourcing a maximum of 0.75 A to the high-voltage transistor while the bottom transistor can sink peak currents up to 2.5 A.

For low currents up to 10 mA, the saturation voltage of the sink darlington transistor is similar to that of a single transistor (see Fig. 10). During switching of this transistor dV/dt is internally limited to reduce interference.

Care should be taken with the external wiring of the output pins to avoid oscillation or interference due to parasitic inductance and wire resistance.

During start-up a small current flows from V<sub>CC</sub> to E2 to precharge the series capacitor at the output (see Fig. 12).

Fig.10 Saturation curve.

TDA8380

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | symbol           | min.        | typ.   | max.  | unit |

|-------------------------------------|------------------|-------------|--------|-------|------|

| Voltage                             |                  |             |        |       |      |

| pin 5 (V <sub>CC</sub> )            |                  | -0.5        |        | 20    | V    |

| pins 1, 2, 4 and 16                 |                  | 0.5         | _      | Vcc   | l v  |

| pins 3 and 13                       |                  | -0.5        | _      | 0.5   | V    |

| pins 7 and 9                        |                  | <b>-0.5</b> | _      | 6.5   | V    |

| pin 11                              |                  | 0.6         | -      | Vcc   | V    |

| Currents                            |                  |             |        | 1     |      |

| pin 5 (V <sub>CC</sub> )            |                  | 0           | _      | 20    | mA   |

| pin 1                               |                  | -0.75       | _      | 0     | Α    |

| pin 2                               |                  | 0           | _      | 0.75  | Α    |

| pins 3, 4, 6 to 8 and 10 to 12      |                  | -10         | -      | 10    | mA   |

| pin 13                              |                  | -200        | _      | 10    | mA   |

| pin 15                              |                  | -2.5        | -      | 0     | Α    |

| pin 16                              |                  | 0           | _      | 2.5   | Α    |

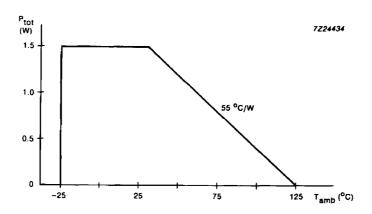

| Total power dissipation             | P <sub>tot</sub> |             | see Fi | g.11  |      |

| Operating ambient temperature range |                  |             |        |       |      |

| (for dissipation ≤ 1 W)             | T <sub>amb</sub> | -25         | -      | + 70  | °C   |

| Storage temperature range           | T <sub>stg</sub> | -55         | _      | + 150 | oC   |

### THERMAL RESISTANCE

From junction to ambient (in free air)

$R_{th j-a(max)} = 55 \text{ K/W}$

Fig.11 Power derating curve.

TDA8380

### **CHARACTERISTICS**

$V_{CC}$  = 14 V;  $T_{amb}$  = 25 °C; reference resistor = 5 k $\Omega$  unless otherwise specified

| parameter                                            | conditions                              | symbol               | min.              | typ.              | max.                | unit     |

|------------------------------------------------------|-----------------------------------------|----------------------|-------------------|-------------------|---------------------|----------|

| Supply                                               |                                         |                      |                   |                   |                     |          |

| Supply voltage                                       |                                         | VCC                  | 9                 | _                 | 20                  | v        |

| Supply initialization level                          |                                         | V <sub>5</sub>       | 15                | 17                | 18                  | v        |

| High voltage protection                              |                                         | V <sub>5</sub>       | 21                | 23                | 25                  | v        |

| Internal fixed minimum<br>protection level           |                                         | <br>  v <sub>5</sub> | 7.9               | 8.4               | 8.9                 | v        |

| Hysteresis                                           |                                         | dVCC                 | -                 | 50                | _                   | mV       |

| Supply current operational before initialization     |                                         | Icc<br>Icc           | -                 | _<br>100          | 15<br>150           | mA<br>μA |

| Reference current (pin 4)                            | note 1                                  | 14                   | 16/5.7            | 16/6              | 16/6.4              | mA       |

| Trigger level V <sub>CCmin</sub> setting             |                                         | V <sub>5</sub>       | 3.6V <sub>4</sub> | 3.8V <sub>4</sub> | _                   | V        |

| Clamp voltage                                        | at 20 mA                                |                      | 21.5              | 23.5              | 25.5                | V        |

| Reference (pin 6)                                    |                                         |                      |                   |                   |                     |          |

| Reference voltage                                    |                                         | V <sub>ref</sub>     | 2.4               | 2.5               | 2.6                 | v        |

| Current range                                        |                                         | I <sub>ref</sub>     | 200               | -                 | 800                 | μΑ       |

| Reference voltage over<br>I <sub>6</sub> range       |                                         | dV <sub>ref</sub>    | -20               | _                 | + 20                | mV       |

| Error amplifier                                      |                                         |                      |                   |                   |                     |          |

| Error amplifier threshold                            | $V_{CC} = 8.5 \text{ to } 20 \text{ V}$ | V <sub>7</sub>       | 2.4               | 2.5               | 2.6                 | v        |

| Input current                                        |                                         | 17                   | o                 | _                 | 5                   | μА       |

| Sink current output                                  | at 1.2 V                                | 18                   | 1                 | _                 | _                   | mA       |

| Source current output                                | at 5.5 V                                | 18                   | 80                | 100               | 130                 | μΑ       |

| Open loop gain                                       |                                         | A0                   | _                 | 100               | _                   | dB       |

| Unity gain bandwidth                                 |                                         | BW                   | _                 | 5                 | _                   | MHz      |

| Input DUTY current                                   | note 1                                  | lg lg                | 16/5.7            | 16/6              | I <sub>6</sub> /6.3 | mA       |

| High FB protection level                             |                                         | V <sub>7</sub>       | 2.95              | 3.1               | 3.25                | v        |

| Temperature coefficient of error amplifier threshold |                                         | dV <sub>7</sub> /dT  | _                 | 100               | _                   | 10-6/    |

| TCG function (see Fig.7)                             |                                         |                      |                   |                   |                     |          |

| Transfer characteristic                              |                                         | dD/dV7               | _                 | 32                | _                   | %/V      |

| Minimum duty factor                                  |                                         | D <sub>min</sub>     | _                 | 12                | _                   | %        |

| Plateau width                                        |                                         | V <sub>7</sub>       | _                 | 200               | _                   | mV       |

**TDA8380**

## **CHARACTERISTICS** (continued)

| parameter                                            | conditions                             | symbol                                                                                                      | min.         | typ.            | max.        | unit     |

|------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|-----------------|-------------|----------|

| Slow-start function                                  |                                        |                                                                                                             |              |                 |             |          |

| Transfer characteristic                              |                                        | dD/dV <sub>12</sub>                                                                                         | _            | 23.8            | _           | %/V      |

| Input current                                        | note 1                                 | 112                                                                                                         | 16/5.7       | 16/6            | 16/6.3      | mA       |

| Sink current during faults                           | at 0.5 V                               | 112                                                                                                         | 8            | _               | _           | mA       |

| Internally fixed maximum<br>duty factor              |                                        | D <sub>max</sub>                                                                                            | 75           | 80              | 85          | <b>%</b> |

| Clamp current                                        | at V <sub>12</sub> = 0.5 V             | 112                                                                                                         | -            | <b>–2</b>       | _           | mA       |

| Output stage                                         |                                        |                                                                                                             |              |                 |             |          |

| Source transistor                                    |                                        |                                                                                                             |              |                 |             |          |

| Voltage drop with respect to VCC                     | at 0.75 A                              | V <sub>CC</sub> -V <sub>1</sub>                                                                             | _            | 2               | _           | V        |

| Pull-up current                                      | $V_{CC} - V_1 = 15 V$                  | -11                                                                                                         | 25           | _               | 100         | μΑ       |

| Operating current range                              |                                        | -1,                                                                                                         | 0            | _               | 0.75        | A        |

| Sink transistor (see Fig. 10)                        |                                        |                                                                                                             |              |                 |             |          |

| Saturation voltage<br>at 2.5 A<br>at 1 A<br>at 10 mA |                                        | V <sub>16</sub> - V <sub>15</sub><br>V <sub>16</sub> - V <sub>15</sub><br>V <sub>16</sub> - V <sub>15</sub> | <br> -<br> - | 2<br>1.5<br>0.3 | _<br>_<br>_ | V<br>V   |

| Leakage current                                      | $V_{16} - V_{15} = 20 V$               | 116                                                                                                         | _            |                 | 1           | μА       |

| Falling edge                                         |                                        | dV <sub>16-15</sub> /dt                                                                                     | _            | 0.2             | -           | V/ns     |

| Operating current range                              |                                        |                                                                                                             |              |                 |             |          |

| Peak                                                 |                                        | 116                                                                                                         | 0            | _               | 2.5         | Α        |

| Average                                              |                                        | 1 <sub>16</sub>                                                                                             | _            | _               | 250         | mA       |

| Oscillator                                           |                                        |                                                                                                             |              | !               |             |          |

| High level voltage                                   |                                        | V <sub>10</sub>                                                                                             |              | 5               | _           | v        |

| Low level voltage                                    |                                        | V <sub>10</sub>                                                                                             | _            | 1.4             | _           | v        |

| Charge current                                       | note 1                                 | 110                                                                                                         | 16/5.7       | 16/6            | 16/6.3      | mA       |

| Frequency range                                      |                                        | fo                                                                                                          | 10           | _               | 100         | kHz      |

| Frequency                                            | $R_6 = 5 k\Omega$<br>$C_{10} = 680 pF$ | fo                                                                                                          | 27           | 28.5            | 30          | kHz      |

| Temperature coefficient of<br>the frequency          |                                        | df/dT                                                                                                       | _            | 100             | _           | 10⁻⁵/K   |

**TDA8380**

| parameter                                           | conditions                                                               | symbol          | min.   | typ.              | max.   | unit |

|-----------------------------------------------------|--------------------------------------------------------------------------|-----------------|--------|-------------------|--------|------|

| Synchronization                                     |                                                                          |                 |        |                   |        |      |

| Minimum synchronization pulse width                 |                                                                          | t11             | _      | -                 | 0.5    | μs   |

| Switching threshold                                 |                                                                          | V <sub>11</sub> | 0.7    | 0.85              | 0.9    | V    |

| Input current                                       |                                                                          | 111             | 2.5    | 5.0               | 7.5    | μΑ   |

| Disabling threshold                                 |                                                                          | V <sub>11</sub> | 4.2    | 5.6               | 6.0    | ٧    |

| Input voltage                                       | at700μA                                                                  | V <sub>11</sub> | 390    | -                 | 550    | mV   |

| Demagnetization input                               |                                                                          |                 |        |                   |        |      |

| Pin voltage                                         | at 0 A                                                                   | V <sub>3</sub>  | -      | 690               | _      | mV   |

| Input current                                       | at 0 V                                                                   | 13              | -30    | -40               | 55     | μΑ   |

| Current range of clamp circuits                     |                                                                          |                 | -10    | -                 | + 10   | mA   |

| Clamp level positive                                | at 10 mA                                                                 | v <sub>3</sub>  | _      | 950               | _      | mV   |

| Clamp level negative                                | at -10 mA                                                                | V <sub>3</sub>  | _      | -800              | -      | mV   |

| Current protection                                  |                                                                          |                 |        |                   |        |      |

| Input current                                       | note 1                                                                   | l <sub>13</sub> | 16/5.7 | I <sub>6</sub> /6 | 16/6.3 | mA   |

| First threshold                                     |                                                                          | V <sub>13</sub> | 190    | 200               | 210    | mV   |

| Second threshold                                    |                                                                          | V <sub>13</sub> | -10    | 0                 | 10     | mV   |

| Delay to switch output via level 1                  | pulse at pin 13<br>from 300 mV to<br>100 mV;<br>I <sub>O</sub> = 500 mA  | _               | _      | 350               | _      | ns   |

| Delay to switch output via level 2                  | pulse at pin 13<br>from 300 mV to<br>-200 mV;<br>I <sub>O</sub> = 500 mA | _               | _      | 300               | 500    | ns   |

| First threshold including $R_{13}$ (12 k $\Omega$ ) | $R_6 = 5 k\Omega$                                                        | _               | _      | -800              | _      | mV   |

| Threshold for open pin detection                    |                                                                          | V <sub>13</sub> | _      | 3.5               | _      | v    |

### Note to the characteristics

1. Over the current range of  $I_6$ ; 200 to 800  $\mu A$ .

Fig.13 Input and output loading diagram.

1136 March 1991