# DATA SHEET

| Part No.         | AN5891K         |

|------------------|-----------------|

| Package Code No. | SDIP024-P-0300B |

# Contents

| ■ Features                                                                 | . 3  |

|----------------------------------------------------------------------------|------|

| ■ Applications                                                             | . 3  |

| ■ Package                                                                  | . 3  |

| ■ Type                                                                     | . 3  |

| ■ Application Circuit Example                                              |      |

| ■ Block Diagram                                                            | . 5  |

| ■ Pin Descriptions                                                         | . 6  |

| ■ Absolute Maximum Ratings                                                 | . 7  |

| ■ Operating Supply Voltage Range                                           | . 7  |

| ■ Electrical Characteristics                                               | . 8  |

| ■ Electrical Characteristics (Reference values for design)                 | . 11 |

| ■ Electrical Characteristics Test Procedures                               | . 14 |

| ■ Electrical Characteristics (Reference values for design) Test Procedures | . 16 |

| ■ Technical Data                                                           | . 17 |

| I/O block circuit diagrams and pin function descriptions                   | . 17 |

| • I <sup>2</sup> C bus                                                     |      |

| Adjust method of AGC control                                               | . 25 |

| Llegge Notes                                                               | 26   |

# AN5891K

# TV and audio sound processor

## ■ Features

- Sound Processor using I<sup>2</sup>C bus

- This IC has Mute, AGC, super bass, tone, volume balance control, and 3-D surround.

### ■ Applications

• TV, Audio

## ■ Package

• 24 pin Plastic Shrink Dual Inline Package (SDIP Type)

#### ■ Type

• Silicon monolithic bipolar IC

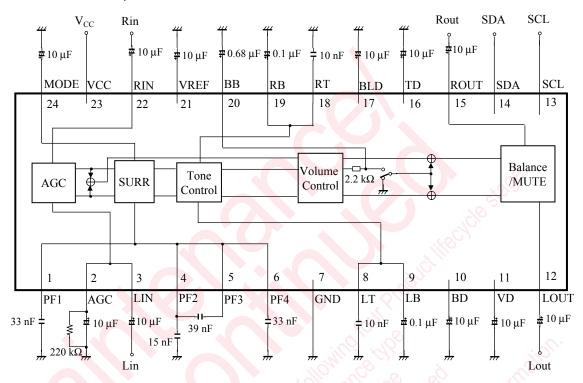

### ■ Application Circuit Example

Application circuit to get L+R output instead of Super Bass Boost

Note) This application circuit is shown as an example but does not guarantee the design for mass production set.

Panasonic

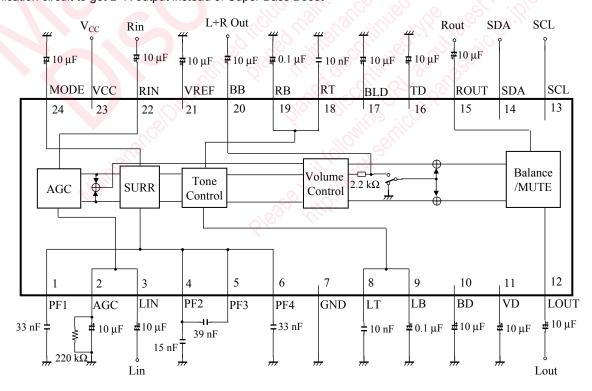

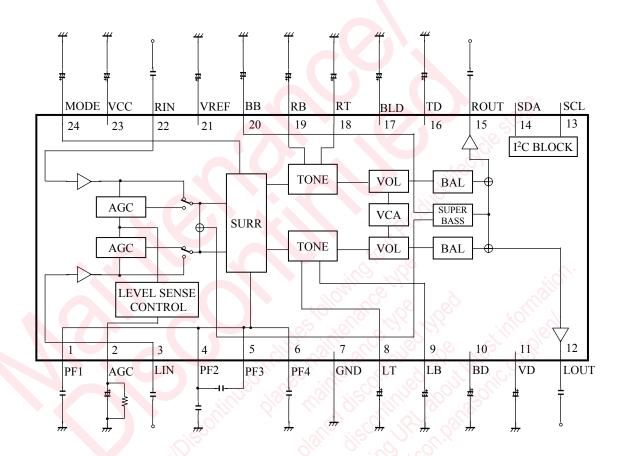

# ■ Block Diagram

AN5891K

Note) This block diagram is for explaining functions. The part of the block diagram may be omitted, or it may be simplified.

**Panasonic**

# ■ Pin Descriptions

| Pin No. | Pin name | Description                         |

|---------|----------|-------------------------------------|

| 1       | PF1      | Phase filter 1                      |

| 2       | AGC      | AGC level sensor                    |

| 3       | LIN      | L-ch. input                         |

| 4       | PF2      | Phase filter 2                      |

| 5       | PF3      | Phase filter 3                      |

| 6       | PF4      | Phase filter 4                      |

| 7       | GND      | Ground                              |

| 8       | LT       | L-ch. treble Fc adjustment          |

| 9       | LB       | L-ch. bass Fc adjustment            |

| 10      | BD       | BASS DAC output                     |

| 11      | VD       | Volume DAC output                   |

| 12      | LOUT     | L-ch. output                        |

| 13      | SCL      | SCL                                 |

| 14      | SDA      | SDA                                 |

| 15      | ROUT     | R-ch. output                        |

| 16      | TD       | Treble DAC output                   |

| 17      | BLD      | Balance DAC output                  |

| 18      | RT       | R-ch. treble Fc adjustment          |

| 19      | RB       | R-ch. bass Fc adjustment            |

| 20      | BB       | Bass mixer gain adjustment          |

| 21      | VREF     | 1/2V <sub>CC</sub>                  |

| 22      | RIN      | R-ch. input                         |

| 23      | VCC      | Power supply pin (V <sub>CC</sub> ) |

| 24      | MODE     | Mode control                        |

## ■ Absolute Maximum Ratings

Note) Absolute maximum ratings are limit values which are not destructed, and are not the values to which operation is guaranteed.

| A No. | Parameter                     | Symbol           | Rating      | Unit | Notes |

|-------|-------------------------------|------------------|-------------|------|-------|

| 1     | Supply voltage                | V <sub>CC</sub>  | 11.0        | V    | *1    |

| 2     | Supply current                | $I_{CC}$         | 50          | mA   | _     |

| 3     | Power dissipation             | $P_{\mathrm{D}}$ | 550         | mW   | _     |

| 4     | Operating ambient temperature | T <sub>opr</sub> | -25 to +75  | °C   | *2    |

| 5     | Storage temperature           | T <sub>stg</sub> | -55 to +150 | °C   | *2    |

Notes) \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

# ■ Operating Supply Voltage Range

| Parameter            | Symbol          | Range       | Unit | Notes |

|----------------------|-----------------|-------------|------|-------|

| Supply voltage range | V <sub>CC</sub> | 6.0 to 10.0 | V    | *     |

Note) \*: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

<sup>\*2 :</sup> Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for T<sub>a</sub> = 25°C.

**Panasonic** AN5891K

# ■ Electrical Characteristics at $V_{CC}$ = 9.0 V Note) $T_a$ = 25°C±2°C unless otherwise specified.

| B   | <b>D</b> .                 |                    | 0 177                                       |        | Limits | Linit    |        |       |

|-----|----------------------------|--------------------|---------------------------------------------|--------|--------|----------|--------|-------|

| No. | Parameter                  | Symbol             | Conditions                                  | Min    | Тур    | Max Unit |        | Notes |

| 1   | Quiescent Current          | I <sub>CC</sub> T  | No input                                    | _      | 45     | 60       | mA     | _     |

| 2   | Volume (Max Level)         | V <sub>Vmax</sub>  | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | -1     | 0      | 1        | dB     | *1    |

| 3   | Volume (Mid Level)         | V <sub>Vmid</sub>  | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | -14.5  | -12.5  | -10.5    | dB     | *1    |

| 4   | Volume (Min Level)         | V <sub>Vmin</sub>  | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     |        | -100   | -90      | dB     | *1    |

| 5   | THD (1 kHz)                | THD <sub>max</sub> | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | -116   | 0.1    | 0.3      | %      | *1    |

| 6   | Max input level            | V <sub>Imax</sub>  | THD = 1%<br>f = 1 kHz                       | 2.0    | 2.2    | _        | V[rms] | *1    |

| 7   | Output noise at volume min | V <sub>Nmin</sub>  | $V_{IN} = 0 V[rms]$ $Rg = 4.7 k\Omega$      | _      | 3      | 10       | μV     | *2    |

| 8   | Output noise at volume max | V <sub>Nmax</sub>  | $V_{IN} = 0 V[rms]$ $Rg = 4.7 k\Omega$      | _      | 65     | 100      | μν     | *2    |

| 9   | Mute Level                 | V <sub>MUTE</sub>  | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | 1/20   | -100   | -90      | dB     | *1    |

| 10  | Balance (Max Level)        | V <sub>Bmax</sub>  | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | -P     | 0      | R        | dB     | *1    |

| 11  | Balance (Min Level)        | $V_{Bmin}$         | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz     | 100 ji | -82    | -80      | dB     | *1    |

| 12  | Bass (Max Level)           | $VB_{Bmax}$        | V <sub>IN</sub> = 400 mV[rms]<br>f = 50 Hz  | 10     | 12.5   | 15       | dB     | _     |

| 13  | Bass (Min Level)           | $VB_{Bmin}$        | V <sub>IN</sub> = 400 mV[rms]<br>f = 50 Hz  | -13.5  | -11.0  | -8.5     | dB     | _     |

| 14  | Treble (Max Level)         | VT <sub>Bmax</sub> | V <sub>IN</sub> = 400 mV[rms]<br>f = 20 kHz | 10     | 12.5   | 15       | dB     | _     |

| 15  | Treble (Min Level)         | $VT_{Bmin}$        | V <sub>IN</sub> = 400 mV[rms]<br>f = 20 kHz | -13.5  | -11.0  | -8.5     | dB     | _     |

| 16  | Super bass (Max Level)     | VX <sub>Bmax</sub> | V <sub>IN</sub> = 400 mV[rms]<br>f = 50 Hz  | 3      | 5      | 7        | dB     | *1    |

| 17  | Super bass (Min Level)     | $VX_{Bmin}$        | V <sub>IN</sub> = 400 mV[rms]<br>f = 50 Hz  | 0      | 2      | 4        | dB     | *1    |

Notes) \*1:DIN AUDIO filter used.

\*2 : A-weighted noise filter used.

# $\blacksquare$ Electrical Characteristics (continued) at $V_{CC}$ = 9.0 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

| В   |                       |                   | 0 :::                                              |           | Limits      |     |         |       |  |

|-----|-----------------------|-------------------|----------------------------------------------------|-----------|-------------|-----|---------|-------|--|

| No. | Parameter             | Symbol            | Conditions                                         | Min       | lin Typ Max |     | Unit    | Notes |  |

| 18  | AGC gain 1            | V <sub>AGC1</sub> | $V_{IN} = 50 \text{ mV}[\text{rms}]$<br>f = 1 kHz  | 77        | 110         | 150 | mV[rms] | *1    |  |

| 19  | AGC gain 2            | V <sub>AGC2</sub> | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz            | 230       | 345         | 470 | mV[rms] | *1    |  |

| 20  | Surround level 1      | $V_{SU1}$         | V <sub>IN</sub> = 50 mV[rms]<br>f = 50 Hz          | 200       | 240         | 280 | mV[rms] | *1    |  |

| 21  | Surround level 2      | $ m V_{SU2}$      | V <sub>IN</sub> = 50 mV[rms]<br>f = 10 kHz         | 130       | 170         | 210 | mV[rms] | *1    |  |

| 22  | Surround noise Level  | V <sub>SN</sub>   | $V_{IN} = 0 \text{ mV}$ $Rg = 4.7 \text{ k}\Omega$ | -         | 110         | 150 | μV[rms] | *2    |  |

| 23  | THD (Surround)        | THD <sub>SU</sub> | V <sub>IN</sub> = 400 mV[rms]<br>f = 1 kHz         | , delcit  | 0.1         | 0.3 | %       | *1    |  |

| 24  | Cross talk            | СТ                | $V_{IN} = 1 V[rms]$<br>f = 1 kHz                   | _         | -78         | -66 | dB      | *2    |  |

| 25  | Channel balance (Max) | CB <sub>max</sub> | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz            | <u>-1</u> | 0           | 1   | dB      | *1    |  |

| 26  | Channel balance (1/4) | CB <sub>1/4</sub> | V <sub>IN</sub> = 1 V[rms]<br>f = 1 kHz            | -2        | 0           | 2   | dB      | *1    |  |

Notes) \*1 : DIN AUDIO filter used.

<sup>\*2 :</sup> A-weighted noise filter used.

**Panasonic** AN5891K

# ■ Electrical Characteristics (continued) at $V_{CC}$ = 9.0 V Note) $T_a$ = 25°C±2°C unless otherwise specified.

| В                | 5 ,                              |                    | 0 1111                                        |     | Limits | Lloit | Notes  |       |

|------------------|----------------------------------|--------------------|-----------------------------------------------|-----|--------|-------|--------|-------|

| No.              | Parameter                        | Symbol             | Conditions                                    | Min | Тур    | Max   | Unit   | Notes |

| I <sup>2</sup> C | Interface                        |                    |                                               |     |        |       |        |       |

| 27               | Suction current during ACK       | I <sub>ACK</sub>   | Max. suction current value of Pin 14 at 0 4 V | 3.0 | 10     | _     | mA     | _     |

| 28               | SCL, SDA signal input High level | $V_{\mathrm{IHI}}$ |                                               | 3.0 | _      | 5.0   | V      | _     |

| 29               | SCL, SDA signal input Low level  | V <sub>ILO</sub>   |                                               | 0   | _      | 1.5   | V      | _     |

| 30               | Max frequency allowable to input | $f_{imax}$         |                                               |     | - >    | 100   | kbit/s |       |

# $\blacksquare$ Electrical Characteristics (Reference values for design) at $V_{CC} = 9.0 \text{ V}$

Note)  $T_a = 25^{\circ}C\pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| B No.               | Deremeter                      | Cumbal              | Conditions                                  | Refe  | erence va   | lues | Unit         | Notes  |  |

|---------------------|--------------------------------|---------------------|---------------------------------------------|-------|-------------|------|--------------|--------|--|

| B NO.               | Parameter                      | Symbol              | Conditions                                  | Min   | Тур         | Max  | Unit         | 140103 |  |

| I <sup>2</sup> C in | terface                        |                     |                                             |       |             |      |              |        |  |

| 1                   | Bus free before start          | t <sub>BUF</sub>    |                                             | 4.0   |             | _    | μs           |        |  |

| 2                   | Set-up time of START condition | t <sub>SU,STA</sub> |                                             | 4.0   | _           | _    | μs           | _      |  |

| 3                   | Hold time of START condition   | t <sub>HD,STA</sub> |                                             | 4.0   |             |      | μs           | _      |  |

| 4                   | Low period of SCL, SDA         | $t_{LO}$            |                                             | 4.0   | <u>-0</u> 6 |      | μs           | _      |  |

| 5                   | High period of SCL             | t <sub>HI</sub>     |                                             | 4.0   |             | _    | μs           | _      |  |

| 6                   | SCL, SDA rise time             | $t_{R}$             |                                             | -1/19 | _           | 1.0  | μs           | _      |  |

| 7                   | SCL, SDA fall time             | $t_{\rm F}$         |                                             |       | _           | 0.35 | μs           | _      |  |

| 8                   | Data set-up time (Write)       | t <sub>SU,DAT</sub> | - 04                                        | 0.25  | _           | _    | μs           | _      |  |

| 9                   | Data hold time (Write)         | t <sub>HD,DAT</sub> |                                             | 0     | _           | _    | μs           | _      |  |

| 10                  | Acknowledge set-up time        | t <sub>SU,ACK</sub> | - ,,0,100,100                               |       | _           | 3.5  | μs           | _      |  |

| 11                  | Acknowledge hold time          | t <sub>HD,ACK</sub> | - MI - S (A)                                | 0     |             |      | μs           | _      |  |

| 12                  | [STOP] condition set-up time   | $t_{\rm SU,STO}$    |                                             | 4.0   |             | it l | μs           | _      |  |

| DAC                 |                                |                     | 185 181 18 18 18 18 18 18 18 18 18 18 18 18 | 131   | 7.10        | 100  |              |        |  |

| 13                  | 6 bit DAC DNLE                 | $L_6$               | 1LSB = [Data (max) – Data (00)]/63          | 0.1   | 1.0         | 1.9  | LSB/<br>STEP | _      |  |

# ■ Electrical Characteristics (Reference values for design) (continued) at V<sub>CC</sub> = 9 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

# $\blacksquare$ Electrical Characteristics (Reference values for design) (continued) at $V_{CC} = 9.0 \ V$

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| B No. | Parameter                             | Symbol            | Conditions                                         | Refe    | erence va | alues    | Unit    | Notes  |  |

|-------|---------------------------------------|-------------------|----------------------------------------------------|---------|-----------|----------|---------|--------|--|

| D NO. | i alametei                            | Symbol            | Conditions                                         | Min Typ |           | Max      | Offic   | 110103 |  |

| 14    | AGC gain 3<br>(Sub address 04H : 05H) | V <sub>AGC3</sub> | $V_{IN} = 100 \text{ mV[rms]}$<br>f = 1 kHz        | _       | 150       | _        | mV[rms] | *1     |  |

| 15    | AGC gain 4<br>(Sub address 04H : 03H) | V <sub>AGC4</sub> | $V_{IN} = 140 \text{ mV}[\text{rms}]$<br>f = 1 kHz |         | 200       | _        | mV[rms] | *1     |  |

| 16    | AGC gain 5<br>(Sub address 04H : 01H) | V <sub>AGC5</sub> | $V_{IN} = 200 \text{ mV}[\text{rms}]$<br>f = 1 kHz |         | 250       | 250X     | mV[rms] | *1     |  |

| 17    | AGC gain 6<br>(Sub address 04H : 07H) | V <sub>AGC6</sub> | $V_{IN} = 280 \text{ mV}[\text{rms}]$<br>f = 1 kHz |         | 350       | <u> </u> | mV[rms] | *1     |  |

| 18    | AGC gain 7<br>(Sub address 04H : 03H) | V <sub>AGC7</sub> | V <sub>IN</sub> = 500 mV[rms]<br>f = 1 kHz         | 180     | 290       | 430      | mV[rms] | *1     |  |

Note) \*1 : DIN AUDIO filter used.

# ■ Electrical Characteristics Test Procedures

| С   | Darameter                  | Cymahal             |      |      | S    | W |    |     | Innut conditions                                          |     | Sub       | addr | ess |     |

|-----|----------------------------|---------------------|------|------|------|---|----|-----|-----------------------------------------------------------|-----|-----------|------|-----|-----|

| No. | Parameter                  | Symbol              | 1    | 2    | 3    | 4 | 5  | 6   | Input conditions                                          | 00H | 01H       | 02H  | 03H | 04H |

| 1   | Quiescent Current          | I <sub>CC</sub> T   | _    | _    |      | _ | ON | OFF | $V_{IN} = 0 \text{ mV}$                                   | FC  | 80        | 77   | 00  | 00  |

| 2   | Volume (Max Level)         | V <sub>Vmax</sub>   | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 V[rms]$<br>f = 1 kHz                          | FC  | 80        | 77   | 00  | 00  |

| 3   | Volume (Mid Level)         | $V_{Vmid}$          | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                  | 80  | 80        | 77   | 00  | 00  |

| 4   | Volume (Min Level)         | $V_{\mathrm{Vmin}}$ | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1  kHz                 | 00  | 80        | 77   | 00  | 00  |

| 5   | THD (1 kHz)                | THD <sub>max</sub>  | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 V[rms]$<br>f = 1 kHz                          | FC  | 80        | 77   | 00  | 00  |

| 6   | Max input level            | V <sub>Imax</sub>   | b, a | a, b | b, a | a | ON | OFF | THD = 1%<br>f = 1 kHz                                     | FC  | 80        | 77   | 00  | 00  |

| 7   | Output noise at volume min | V <sub>Nmin</sub>   | c    | c    | b, a | b | ON | OFF | $V_{IN} = 0 \text{ mV}$ $Rg = 4.7 \text{ k}\Omega$        | 00  | 80        | 77   | 00  | 00  |

| 8   | Output noise at volume max | V <sub>Nmax</sub>   | c    | c    | b, a | b | ON | OFF | $V_{IN} = 0 \text{ mV}$ $Rg = 4.7 \text{ k}\Omega$        | FC  | 80        | 77   | 00  | 00  |

| 9   | Mute Level                 | V <sub>MUTE</sub>   | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                  | FE  | 80        | 77   | 00  | 00  |

| 10  | Balance (Max Level)        | V <sub>Bmax</sub>   | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 V[rms]$<br>f = 1 kHz                          | FC  | FC,<br>00 | 77   | 00  | 00  |

| 11  | Balance (Min Level)        | $V_{Bmin}$          | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                  | FC  | FC,<br>00 | 77   | 00  | 00  |

| 12  | Bass (Max Level)           | $VB_{Bmax}$         | b, a | a, b | b, a | c | ON | OFF | $V_{IN} = 400 \text{ mV}[\text{rms}]$<br>f = 50 Hz        | FC  | 80        | 7F   | 00  | 00  |

| 13  | Bass (Min Level)           | $VB_{Bmin}$         | b, a | a, b | b, a | c | ON | OFF | $V_{IN} = 400 \text{ mV}[\text{rms}]$<br>f = 50 Hz        | FC  | 80        | 70   | 00  | 00  |

| 14  | Treble (Max Level)         | $VT_{Bmax}$         | b, a | a, b | b, a | c | ON | OFF | $V_{IN} = 400 \text{ mV}[\text{rms}]$<br>f = 20 kHz       | FC  | 80        | F7   | 00  | 00  |

| 15  | Treble (Min Level)         | $VT_{Bmin}$         | b, a | a, b | b, a | ç | ON | OFF | $V_{IN} = 400 \text{ mV[rms]}$<br>f = 20 kHz              | FC  | 80        | 07   | 00  | 00  |

| 16  | Super bass (Max Level)     | VX <sub>Bmax</sub>  | b, a | a, b | b, a | c | ON | OFF | $V_{IN} = 400 \text{ mV[rms]}$ $f = 50 \text{ Hz}$        | FD  | 80        | 77   | 00  | 00  |

| 17  | Super bass (Min Level)     | $VX_{Bmin}$         | b, a | a, b | b, a | c | ON | OFF | $V_{IN} = 400 \text{ mV}[\text{rms}]$ $f = 50 \text{ Hz}$ | FD  | 83        | 77   | 00  | 00  |

# ■ Electrical Characteristics Test Procedures (continued)

| С   | Darameter             | Cumhal            |      |      | S    | W |    |     | Innut conditions                                        | Sub address |     |     |     |     |

|-----|-----------------------|-------------------|------|------|------|---|----|-----|---------------------------------------------------------|-------------|-----|-----|-----|-----|

| No. | Parameter             | Symbol            | 1    | 2    | 3    | 4 | 5  | 6   | Input conditions                                        | 00H         | 01H | 02H | 03H | 04H |

| 18  | AGC gain 1            | V <sub>AGC1</sub> | b, a | a, b | a, b | a | ON | OFF | $V_{IN} = 50 \text{ mV}[\text{rms}]$<br>f = 1 kHz       | FC          | 80  | 77  | 00  | 03  |

| 19  | AGC gain 2            | V <sub>AGC2</sub> | b, a | a, b | a, b | a | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                | FC          | 80  | 77  | 00  | 03  |

| 20  | Surround level 1      | V <sub>SU1</sub>  | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 50 \text{ mV}[\text{rms}]$<br>f = 50 Hz       | FC          | 80  | 77  | 80  | 00  |

| 21  | Surround level 2      | V <sub>SU2</sub>  | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 50 \text{ mV[rms]}$<br>f = 10 kHz             | FC          | 80  | 77  | 80  | 00  |

| 22  | Surround noise Level  | V <sub>SN</sub>   | c    | c    | b, a | ь | ON | OFF | $V_{IN} = 0 \text{ mV[rms]}$ $Rg = 4.7 \text{ k}\Omega$ | FC          | 80  | 77  | 80  | 00  |

| 23  | THD (Surround)        | THD <sub>SU</sub> | b, a | a, b | a    | a | ON | OFF | $V_{IN} = 400 \text{ mV[rms]}$<br>f = 1 kHz             | FC          | 80  | 77  | 80  | 00  |

| 24  | Cross talk            | СТ                | b, a | a, b | a, b | b | ON | OFF | $V_{IN} = 1 V[rms]$<br>f = 1 kHz                        | FC          | 80  | 77  | 00  | 00  |

| 25  | Channel balance (Max) | CB <sub>max</sub> | =(   |      |      |   | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                | FC          | 80  | 77  | 00  | 00  |

| 26  | Channel balance (1/4) | CB <sub>1/4</sub> |      |      |      |   | ON | OFF | $V_{IN} = 1 \text{ V[rms]}$<br>f = 1 kHz                | 40          | 80  | 77  | 00  | 00  |

# ■ Electrical Characteristics (Reference values for design) Test Procedures

| С   | Parameter  | Symbol            | SW   |      |      |   |    |     | Innut conditions                                    | Sub address |     |     |     |     |

|-----|------------|-------------------|------|------|------|---|----|-----|-----------------------------------------------------|-------------|-----|-----|-----|-----|

| No. | Parameter  | Symbol            | 1    | 2    | 3    | 4 | 5  | 6   | Input conditions                                    | 00H         | 01H | 02H | 03H | 04H |

| 14  | AGC gain 3 | V <sub>AGC3</sub> | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 100 \text{ mV}[\text{rms}]$<br>f = 1 kHz  | FC          | 80  | 77  | 00  | 05  |

| 15  | AGC gain 4 | V <sub>AGC4</sub> | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 140 \text{ mV}[\text{rms}]$<br>f = 1 kHz  | FC          | 80  | 77  | 00  | 03  |

| 16  | AGC gain 5 | V <sub>AGC5</sub> | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 200 \text{ mV}[\text{rms}]$<br>f = 1 kHz  | FC          | 80  | 77  | 00  | 01  |

| 17  | AGC gain 6 | V <sub>AGC6</sub> | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 280 \text{ mV[rms]}$<br>f = 1 kHz         | FC          | 80  | 77  | 00  | 07  |

| 18  | AGC gain 7 | V <sub>AGC7</sub> | b, a | a, b | b, a | a | ON | OFF | $V_{IN} = 500 \text{ mV}[\text{rms}]$<br>f = 1  kHz | FC          | 80  | 77  | 00  | 03  |

# ■ Technical Data

• I/O block circuit diagrams and pin function descriptions

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

| Pin<br>No. | Waveform and voltage                       | Internal circuit                 | Description      |

|------------|--------------------------------------------|----------------------------------|------------------|

| 1          | 4.5 V                                      | 5k 2k                            | Phase filter 1   |

| 2          | Depend on input<br>level<br>0.5 V to 2.0 V | Level 2 Level 1  1k U50kU2k  2   | AGC level sensor |

| 3          | 4.5 V                                      | 3<br>1.5k<br>1/2 V <sub>CC</sub> | L-ch. input      |

| 4          | 4.5 V                                      | 4 2.5k                           | Phase filter 2   |

| 5          | 4.5 V                                      | 3 2k 2k 2k 2.5k 1                | Phase filter 3   |

• I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

| Pin<br>No. | Waveform and voltage                                 | Internal circuit                                       | Description                |

|------------|------------------------------------------------------|--------------------------------------------------------|----------------------------|

| 6          | 4.5 V                                                | 6 5k 2k                                                | Phase filter 4             |

| 7          | 0 V                                                  |                                                        | GND                        |

| 8          | 4.5 V                                                | 8 900                                                  | L-ch. Treble Fc adjustment |

| 9          | 4.5 V                                                | 8.64k<br>1.36k<br>———————————————————————————————————— | L-ch. Bass Fc adjustment   |

| 10         | Depend on I <sup>2</sup> C<br>data<br>1.6 V to 2.5 V | 250<br>19.4k<br>72.0 V                                 | Bass DAC output            |

• I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

| Pin<br>No. | Waveform and voltage                                 | Internal circuit | Description                      |

|------------|------------------------------------------------------|------------------|----------------------------------|

| 11         | Depend on I <sup>2</sup> C<br>data<br>2.0 V to 4.0 V | 3.5 V 11k 600    | Volume DAC output                |

| 12         | 4.5 V                                                | 250              | L-ch. output                     |

| 13         |                                                      | 2k               | I <sup>2</sup> C bus clock input |

| 14         | -                                                    | 2k 15p           | I <sup>2</sup> C bus data input  |

| 15         | 4.5 V                                                | 250              | R-ch. output                     |

• I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

| Pin<br>No. | Waveform and voltage                                 | Internal circuit               | Description                |

|------------|------------------------------------------------------|--------------------------------|----------------------------|

| 16         | Depend on I <sup>2</sup> C<br>data<br>1.6 V to 2.5 V | 250<br>16<br>250<br>19.4k      | Treble DAC output          |

| 17         | Depend on I <sup>2</sup> C<br>data<br>2.5 V to 3.5 V | 3.5 V 15k (17) 250 250 250 250 | Balance DAC output         |

| 18         | 4.5 V                                                | 18 900 6.3k                    | R-ch. Treble Fc adjustment |

| 19         | 4.5 V                                                | 8.64k<br>11.36k                | R-ch. Bass Fc adjustment   |

| 20         | 4.5 V                                                | 2.2k 2k 2k                     | Bass mix gain adjustment   |

• I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

| Pin<br>No. | Waveform and voltage                                 | Internal circuit                 | Description                   |

|------------|------------------------------------------------------|----------------------------------|-------------------------------|

| 21         | 4.5 V                                                | 21 70k 500 70k                   | Reference voltage stabilizing |

| 22         | 4.5 V                                                | 22<br>1.5k<br>1/2V <sub>CC</sub> | R-ch. input                   |

| 23         | 9.0 V                                                | - "iges "ilitelings"             | $V_{CC}$                      |

| 24         | Depend on I <sup>2</sup> C<br>data<br>0.6 V to 2.6 V | 30.8k 24                         | Mode control                  |

# ■ Technical Data (continued)

• I2C-bus

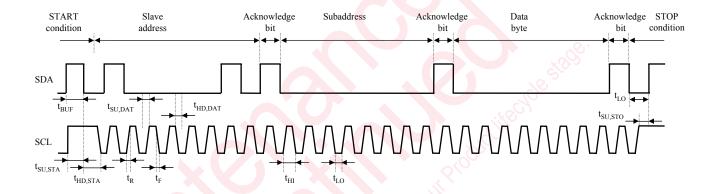

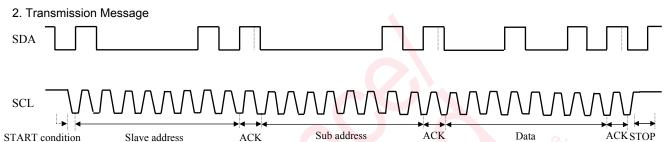

Fig.1 Example of transmission message

For transmission messages, both SCL and SDA are transferred in the form of synchronized serial transmission.

SCL is a clock of a specific frequency, and SDA indicates address data for controlling the receiving side and is transferred in parallel, being synchronized with SCL.

Data is transferred in principle in 3 octets (bytes), and each one octet (one octet = 8 bits) includes one acknowledge bit.

Frame structure is described below.

#### (a) START condition

The receiver becomes possible to receive data when SDA changes from High to Low while SCL is High.

#### (b) STOP condition

The receiver halts receiving when SDA changes from Low to High while SCL is High.

#### (c) Slave address

This is an address which is determined for each device. If other device address is sent, receiving will be halted.

#### (d) Sub address

This is an address which is determined for each function.

#### (e) Data

This is control data.

#### (f) Acknowledge bit

This is a bit by which the master acknowledges that data was successfully received in each octet. Master sends the High signal and the receiver sends back the Low signal as shown in Figure 1 with dotted line, causing the master to acknowledge the reception by the receiver. If the Low signal is not returned, communication will be halted. Except START and STOP conditions, SDA does not change while SCL is High.

SDB00169AEB 22

condition

# ■ Technical Data (continued)

- I2C-bus (continued)

- 3. I2C Bus Addressing

- (1) This contains 7 DAC controls and 4 SWs.

- (2) オートインクリメント機能は以下のとおりです。

- Sub address 0xxxxxxx : Auto-increment mode

(When the data is sent in consecutive order, the Sub address will be changed in consecutive order, as data is input.)

• Sub address 1xxxxxxx : Data update mode (When the data is sent consecutively, it is sent to the same Sub address.)

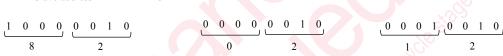

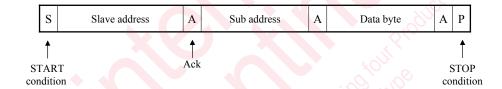

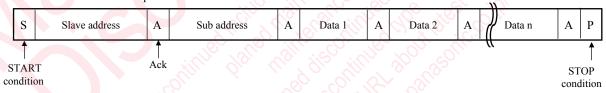

(3) I<sup>2</sup>C bus protocol

• Slave address: 10000010 (82H)

• Format (Usual)

• Auto increment mode/Data update mode

(4) Since the DAC initial status is not guaranteed, the standard data input is certainly necessary when power is turned ON.

# ■ Technical Data (continued)

- I<sup>2</sup>C-bus (continued)

- 3. I<sup>2</sup>C Bus Addressing (continued)

- (5) Sub address byte and data byte format

| Sub     | Upper MSB Data byte     |    |    |    |       |     |          |                      |  |

|---------|-------------------------|----|----|----|-------|-----|----------|----------------------|--|

| address | D7                      | D6 | D5 | D4 | D3    | D2  | D1       | D0                   |  |

| 00      |                         |    |    |    |       |     |          | Super Bass<br>ON/OFF |  |

| 01      | Balance BASS Mix Effect |    |    |    |       |     |          |                      |  |

| 02      | L/R Treble L/R Bass     |    |    |    |       |     | •        |                      |  |

| 03      | MODE × × Surround E.    |    |    |    |       |     | d Effect |                      |  |

| 04      | Not defined             |    |    |    | \$100 | AGC | ADJ      | AGC<br>ON/OFF        |  |

1) MODE

"00" = Bypass

"01" = Simulated Stereo

"10" = Stereo Surround

"11" = Mono surround

2) Volume

DATA = "0000000" : min

DATA = "111111" : max

3) Balance

DATA = "000000" : Lout : min, Rout : max

DATA = "100000" : CENTER

DATA = "111111" : Lout : max, Rout : min

4) L/R Treble, Bass

DATA = "0000" : min

DATA = "0111" : CENTER

DATA = "1111" : max

5) Mute ON/OFF

DATA = "0" : OFF

DATA = "1" : ON

6) Bass Mix ON/OFF

DATA = "0" : OFF

DATA = "1" : ON

7) Bass Mix Effect

DATA = "11" : min

DATA = "00" : max

8) AGC ON/OFF

DATA = "0" : OFF

DATA = "1" : ON

9) AGC ADJ (0 dB Adjustment) \*

DATA = "00" : 200 mV[rms]

DATA = "01" : 140 mV[rms]

DATA = "10" : 100 mV[rms]

DATA = "11" : 280 mV[rms]

10) Surround Effect

DATA = "1111" : min

DATA = "0000" : max

Note) \*: 0 dB Adjustment level of AGC is reference value, and not guaranteed by shipping inspection.

# ■ Technical Data (continued)

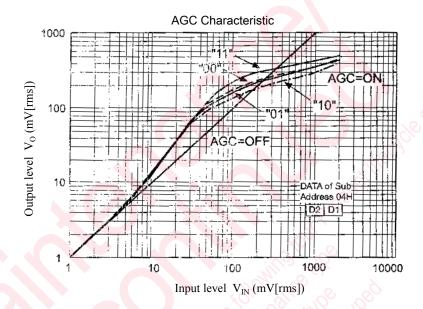

• Adjust method of AGC control

AGCがONの場合,入出力ゲインは小信号レベルにおいては0dB,標準信号レベルでは上昇し,大信号レベルでは減少します。また,AGCの入出力特性は下記のとおり $I^2C$ によって制御できます。

#### ■ Usage Notes

- Special attention and precaution in using

- 1. This IC is intended to be used for general electronic equipment [Television].

- Consult our sales staff in advance for information on the following applications:

- Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as for automobile, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others: Applications of which reliability equivalent to (1) to (7) is required

- 2. Pay attention to the direction of LSI. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might smoke or ignite.

- 3. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 4. Perform a visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as a solder-bridge between the pins of the semiconductor device. Also, perform a full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the LSI during transportation.

- 5. Take notice in the use of this product that it might break or occasionally smoke when an abnormal state occurs such as output pin-V<sub>CC</sub> short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short).

And, safety measures such as an installation of fuses are recommended because the extent of the above-mentioned damage and smoke emission will depend on the current capability of the power supply.

- 6. When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- 7. When using the LSI for new models, verify the safety including the long-term reliability for each product.

- 8. When the application system is designed by using this LSI, be sure to confirm notes in this book. Be sure to read the notes to descriptions and the usage notes in the book.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805